# **TECHNICAL MANUAL**

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL

MULTIPLEXER TD-976/G (NSN 7025-01-048-9678)

This copy is a reprint which includes current pages from Changes 1 and 2.

HEADQUARTERS, DEPARTMENT OF THE ARMY

**JANUARY 1980**

#### **WARNINGS**

Potentially *lethal* voltages are present within the TD-976/G and the TD-982/G. These voltages can be present within the TD-976/G even when the equipment is turned off. Always observe the WARNINGS and CAUTIONS throughout the manual when making electrical interconnections and performing maintenance functions within the TD-976/G.

#### 115 VOLTS AC

The 115-volt ac primary power is always applied to TB1 in the card file and to S9 on the front panel when the power cable is connected between the ac power source and the TD-976/G. Always disconnect the power cable when working in the TD-976/G.

#### **400 VOLTS DC**

Cable drive power of 400 volts dc with a constant current of 45 milliamperes may be present in the equipment when the POWER IN and POWER OUT indicators are lit. The high voltage can be generated within the unit or the voltage may be applied from another TD-976/G that is connected to the unit being serviced.

#### HIGH-VOLTAGE CAPACITORS

Wait at least 15 seconds after cable power is removed from the TD-976/G to ensure that high-voltage capacitors in the unit are discharged.

| CHANGE ) | HEADQUARTERS                  |

|----------|-------------------------------|

|          | DEPARTMENT OF THE ARMY        |

| No. 2 )  | WASHINGTON, DC, 29 April 1983 |

# **Direct Support And General Support**

# **Maintenance Manual**

# MULTIPLEXER TD-976/G (NSN 7025-01-048-9678)

TM 11-7025-202-34, 31 January 1980 is changed as follows:

- 1. New or changed material is indicated by a vertical bar in the margin of the page.

- 2. Remove old pages and insert new pages as indicated below:

Remove Insert

None 1-0

3. File this change sheet in front of the publication for reference purposes.

| Βv | Order | of | the | Secretary | of / | the | Arm | ۷: |

|----|-------|----|-----|-----------|------|-----|-----|----|

|----|-------|----|-----|-----------|------|-----|-----|----|

EDWARD C. MEYER General, United States Army Chief of Staff

Official:

ROBERT M. JOYCE Major General, United States Army The Adjutant General

# DISTRIBUTION:

To be distributed in accordance with Special List.

**CHANGE**

NO. 1

HEADQUARTERS

DEPARTMENT OF THE ARMY

WASHINGTON, DC,16 March 1981

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL

# MULTIPLEXER TD-976/G (NSN 7025-01-048-9678)

TM 11-7025-202-34, 31 January 1980 is changed as follows:

- 1. Remove old pages and insert new pages as indicated below.

- 2. New or changed material is indicated by a vertical bar in the margin of the page.

- 3. Added or revised illustrations are indicated by a vertical bar adjacent to the illustration identification number.

| Remove Pages               | Insert Pages               |

|----------------------------|----------------------------|

| i through iv               | i through iv               |

| 2-55 and 2-56              | 2-55 and 2-56              |

| 2-107 through 2-110        | 2-107 through 2-110        |

| 2-115 through 2-118        | 2-115 through 2-118        |

| 3-3 and 3-4                | 3-3 and 3-4                |

| 3-19 and 3-20              | 3-19 and 3-20              |

| 3-27 and 3-28              | 3-27 and 3-28              |

| 3-43 and 3-44              | 3-43 and 3-44              |

| None                       | 3-44.1/3-44.2              |

| 3-45 through 3-62          | 3-45 through 3-62          |

| 3-65 and 3-66              | 3-65 and 3-66              |

| 3-87 through 3-94          | 3-87 through 3-94          |

| 4-1 and 4-2                | 4-1 and 4-2                |

| None                       | 4-2.1/4-2.2                |

| 4-5 and 4-6                | 4-5 and 4-6                |

| 4-11 and 4-12              | 4-11 and 4-12              |

| 4-15 and 4-16              | 4-15 and 4-16              |

| 4-19 and 4-20              | 4-19 and 4-20              |

| 4-23 and 4-24              | 4-23 and 4-24              |

| None                       | 4-24.1/4-24.2              |

| 4-25 and 4-26              | 4-25 and 4-26              |

| A-1                        | A-1                        |

| Glossary-1                 | Glossary-1                 |

| Index-1 through Index-6    | Index-1 through Index-6    |

| FO-3 (sheet 2)             | FO-3 (sheet 2)             |

| FO-6 (sheet 1)             | FO-6 (sheet 1)             |

| FO-6 (sheets 3 and 4)      | FO-6 (sheets 3 and 4)      |

| FO-9 (sheet 3)'            | FO-9 (sheet 3)             |

| FO-10 (sheets 2 through 4) | FO-10 (sheets 2 through 4) |

| FO-14 (sheet 1)            | FO-14 (sheet 1)            |

| FO-17 (sheet 1)            | FO-17 (sheet 1)            |

| FO-20 (sheet 1)            | FO-20 (sheet 1)            |

File this change sheet in front of the publication for reference purposes.

# E. C. MEYER General, United States Army Chief of Staff

# Official:

J. C. PENNINGTON Major General, United States Army The A 4dutant General

#### Distribution:

USAR: None

Active Army: HISA (Ft Monmouth) (21) USAINSCOM (2) COE (1) **TSG** (1) **USAARENBD** (1) DARCOM (1) TRADOC (2) OS Ma Cmd (4) TEOOM (2) USACC (4) MDW (1) Armies (2) Corps (2) Svc Colleges (1) USASIGS (5) USAADS (2) USAFAS (2) USAARMS (2) USAIS (2) NG: None

For explanation of abbreviations used, see AR 310-50.

Ft Gillem (10) USA Dep (1) Sig Sec USA Dep (1)

USAES (2)

USAICS (3)

USARMIŚ (1)

Ft Carson (5)

SAAD (30)

**TOAD (14)**

SHAD (2)

USAERDAA (1)

**USAERDAW (1)** Ft Gordon (10)

Army Dep (1) except

MAAG (1)

Ft Richardson (CERCOM Ofc) (2) Units org under fol TOE:

29-207 (2) 29-610 (2)

Dorograph

No. 11-7025-202-34

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL MULTIPLEXER TD-976/G (NSN 7025-01-048-9678)

## **REPORTING OF ERRORS**

You can improve this manual by recommending improvements using DA Form 2028-2 located in the back of the manual. Simply tear out the self-addressed form, fill it out as shown on the sample, fold it where shown, and drop it in the mail.

If there are no blank DA Forms 2028-2 in the back of your manual, use the standard DA Form 2028 (Recommended Changes to Publications and Blank Forms) and forward to the Commander, US Army Communications and Electronics Material Readiness Command, ATTN: DRSEL-ME-MQ, Fort Monmouth, NJ 07703.

In either case a reply will be furnished direct to you.

|            |                                                     | Faragrapii      | raye  |

|------------|-----------------------------------------------------|-----------------|-------|

| CHAPTER 1. | INTRODUCTION                                        |                 |       |

| Section I. | General                                             | 1-1             | 1-1   |

| II.        | Description and data                                | 1-6             | 1-1   |

| CHAPTER 2. | FUNCTIONING OF EQUIPMENT                            |                 |       |

| Section I. | Introduction                                        | 2-1             | 2-1   |

| II.        | SG message formats                                  | 2-5             | 2-3   |

| III.       | Basic equipment concepts                            | 2-8             | 2-6   |

| IV.        | Overall block diagram discussion                    | 2-12            | 2-10  |

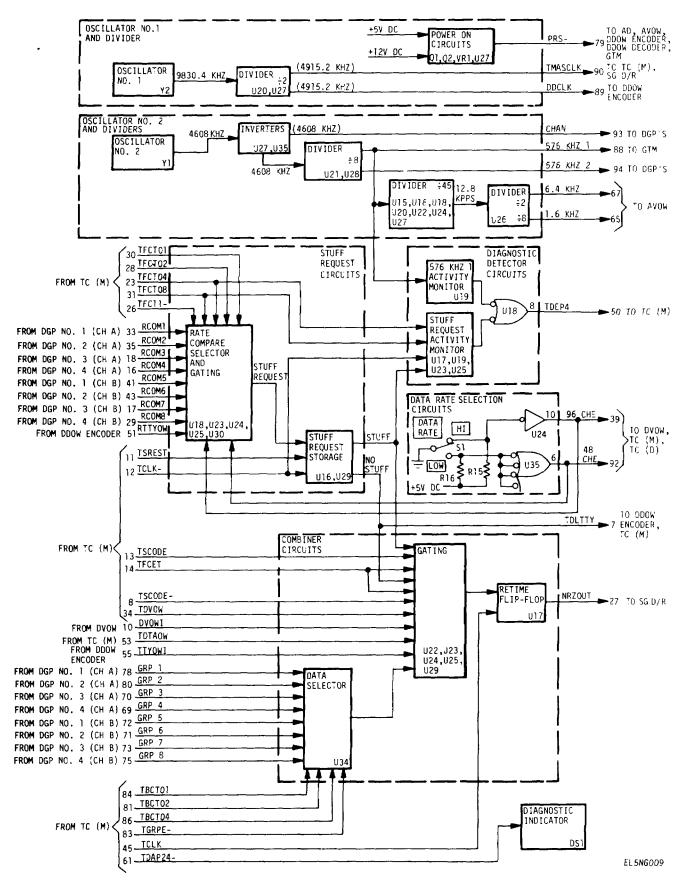

| V.         | Master oscillator/combiner (MO/C) card 21A4         | 2-18            | 2-24  |

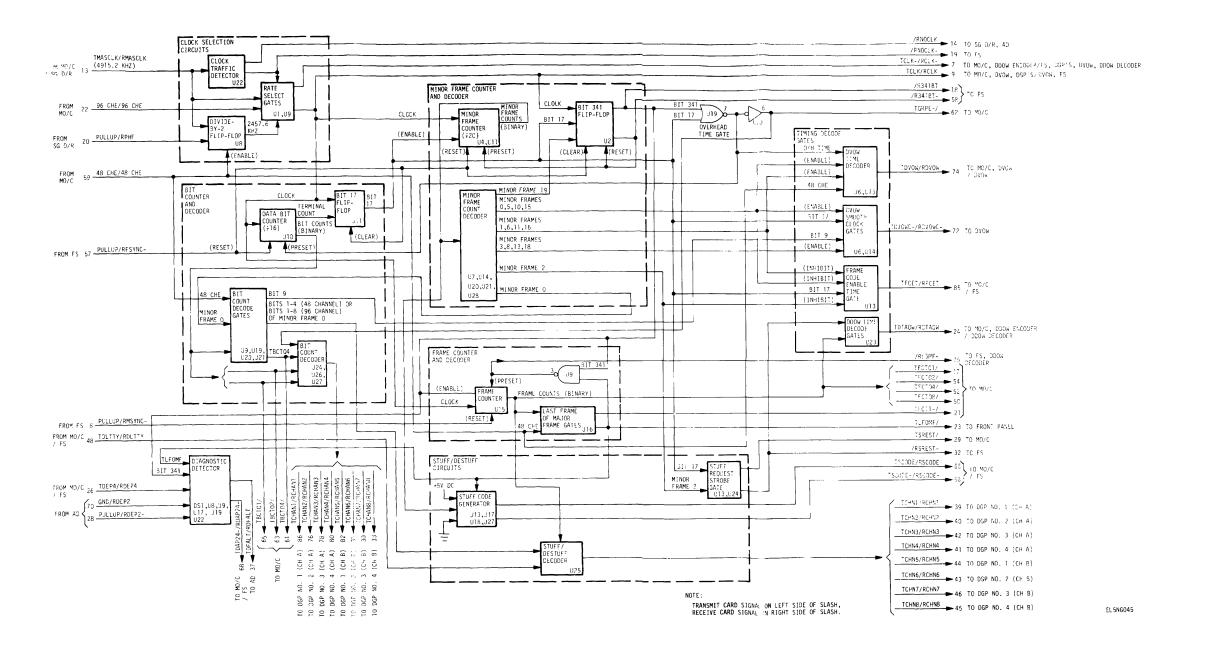

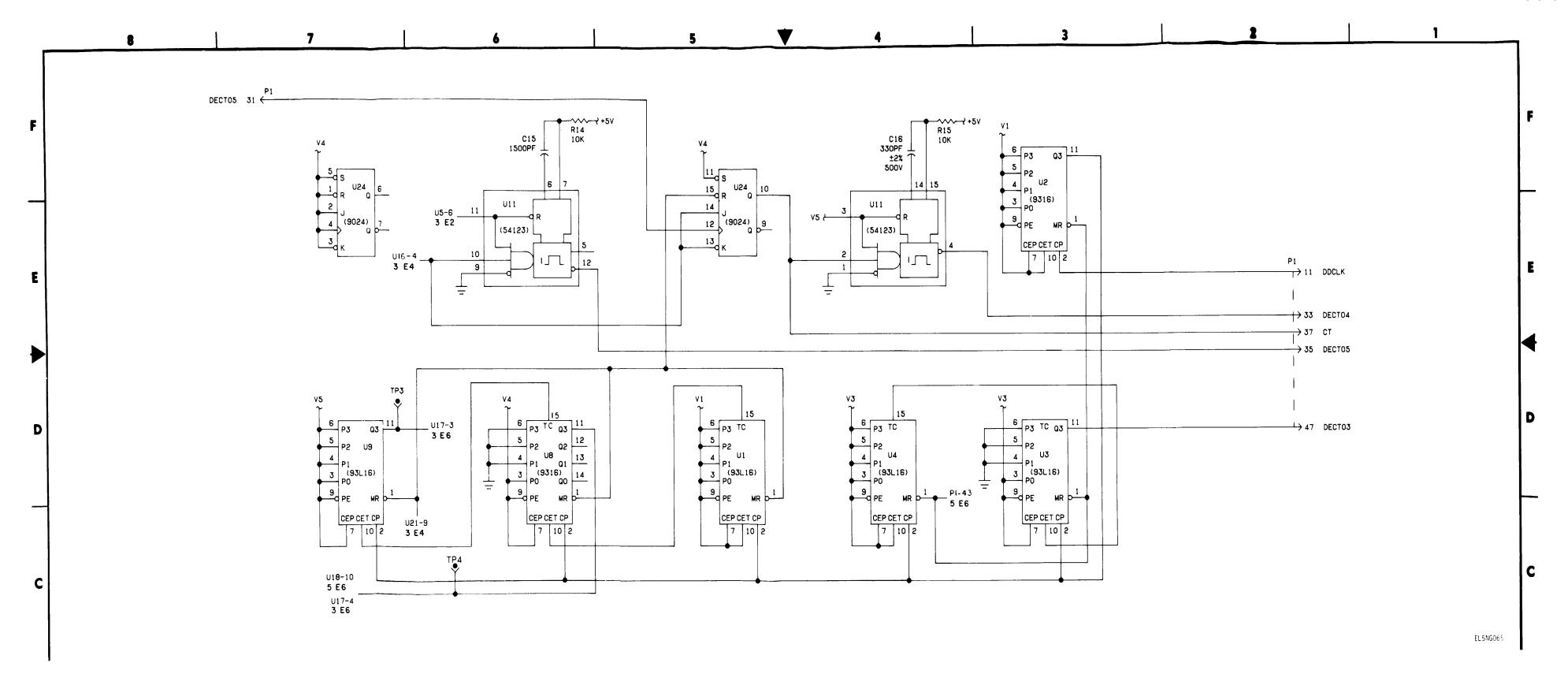

| VI.        | Timing and control (TC) card 21A5                   | 2-21            | 2-31  |

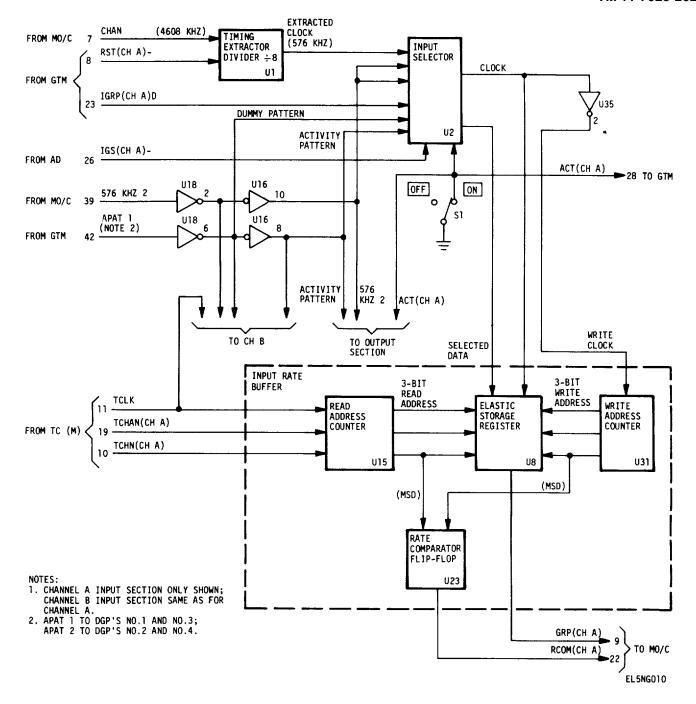

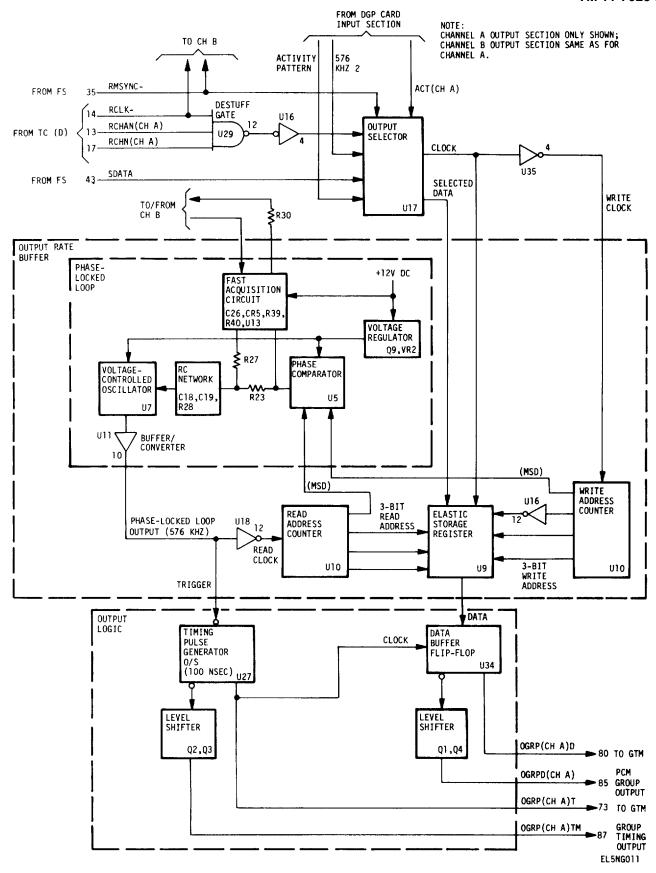

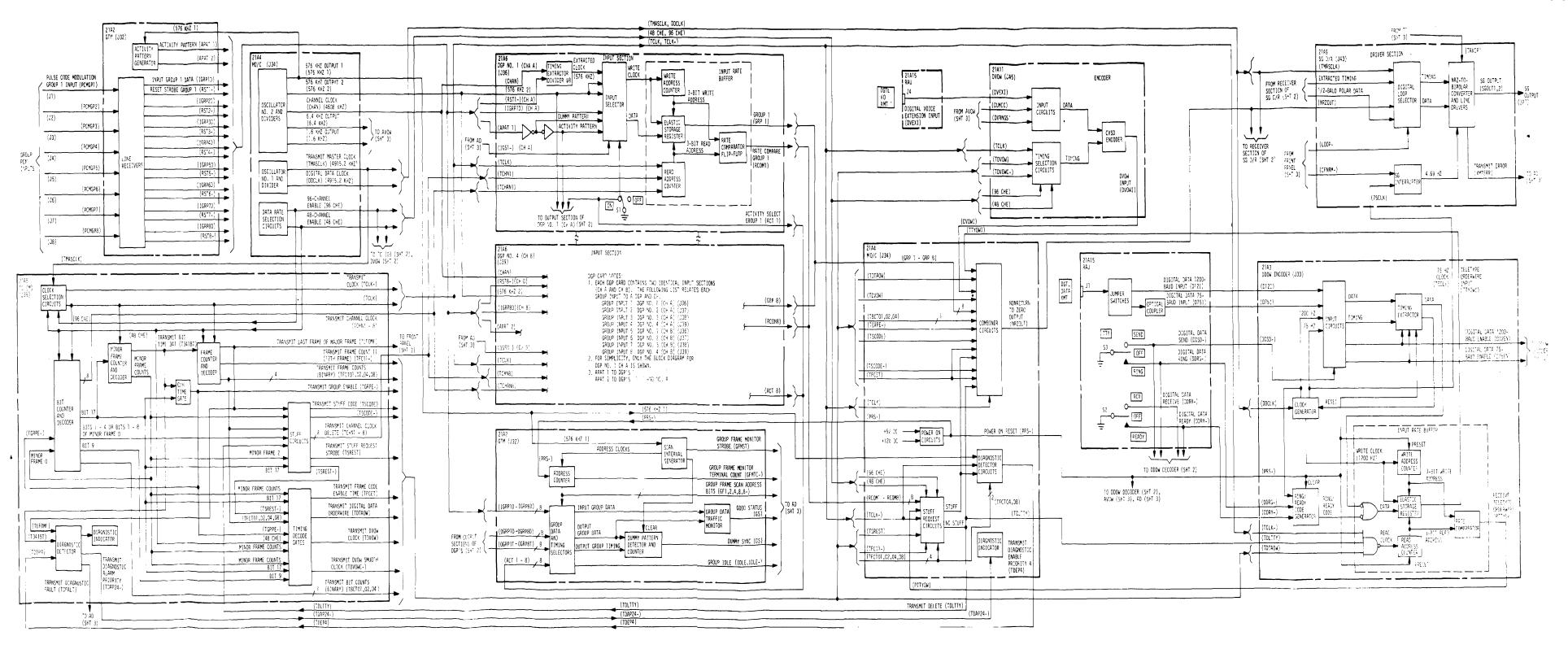

| VII.       | Dual group processor (DGP) card 21A6                | 2-24            | 2-40  |

| VIII.      | Digital voice orderwire (DVOW) card 21A11           | 2-29            | 2-50  |

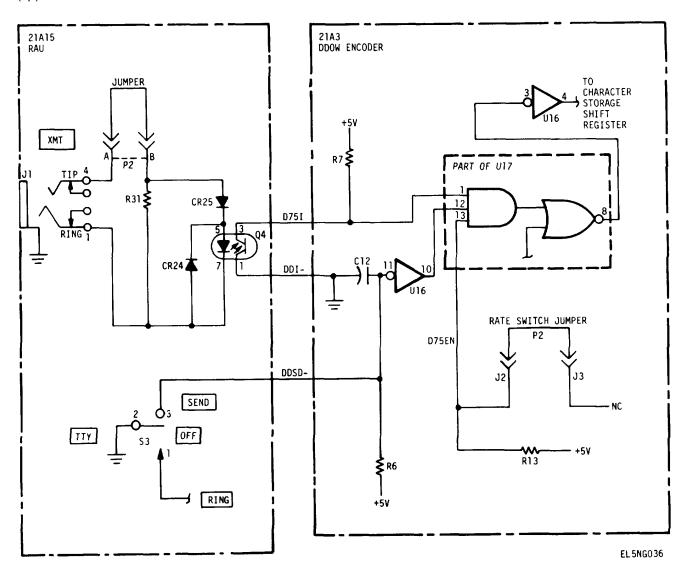

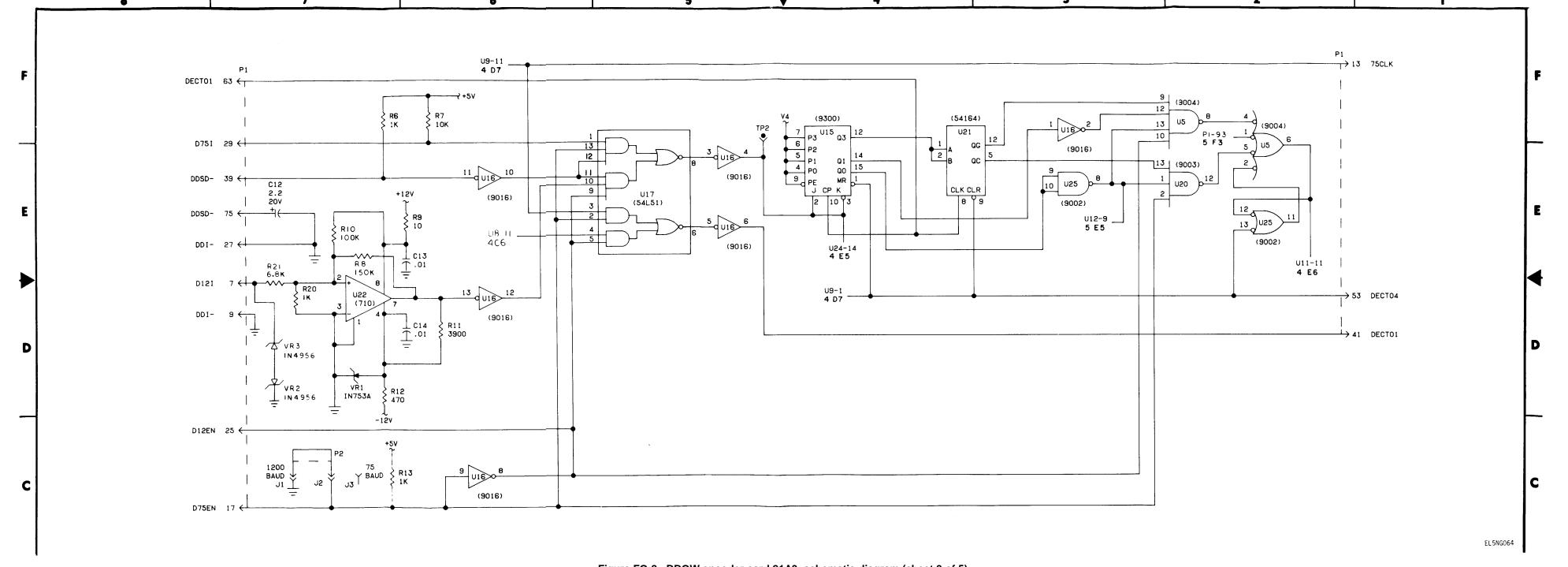

| IX.        | Digital data orderwire (DDOW) encoder card 21A3     | 2-34            | 2-62  |

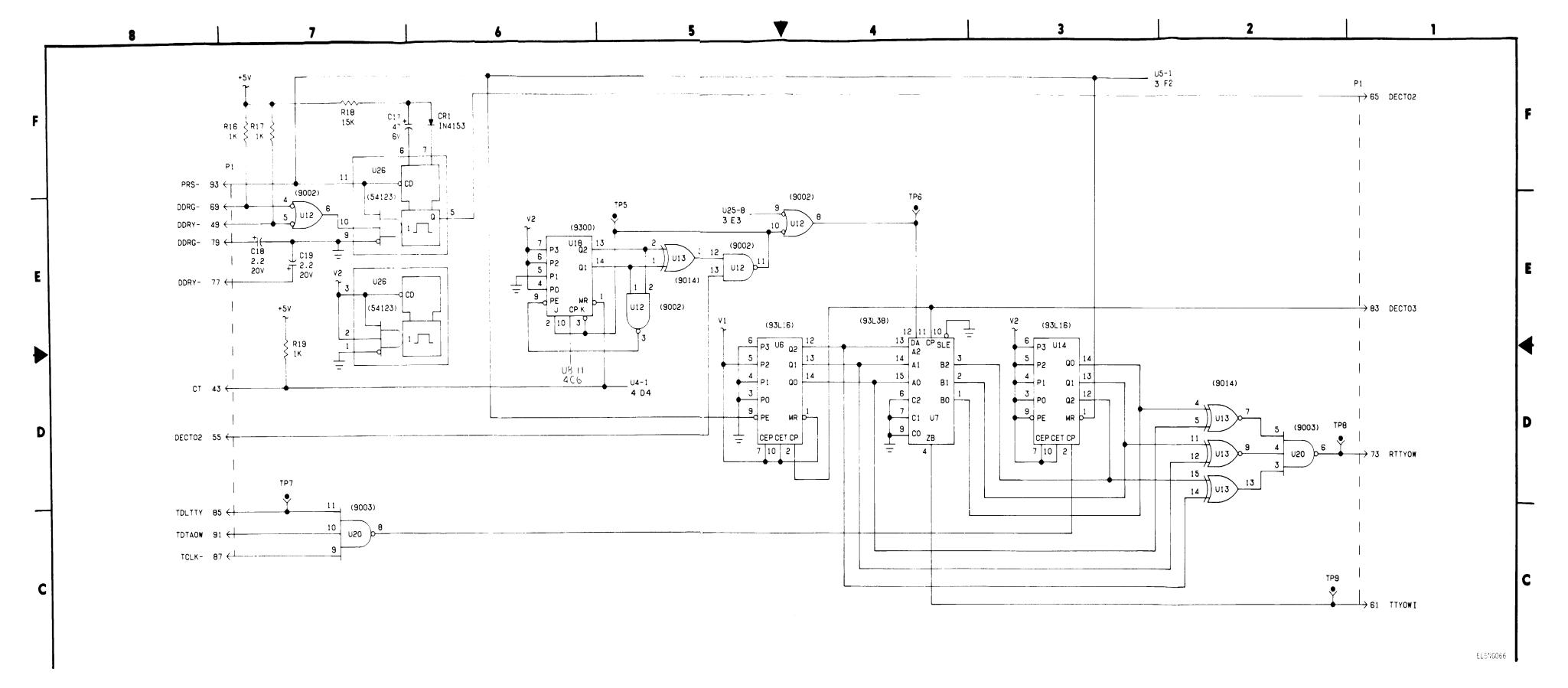

| X.         | Digital data orderwire (DDOW) decoder card 21A8     | 2-38            | 2-70  |

| XI.        | Supergroup driver/receiver (SG D/R) card 21A9       | 2-41            | 2-77  |

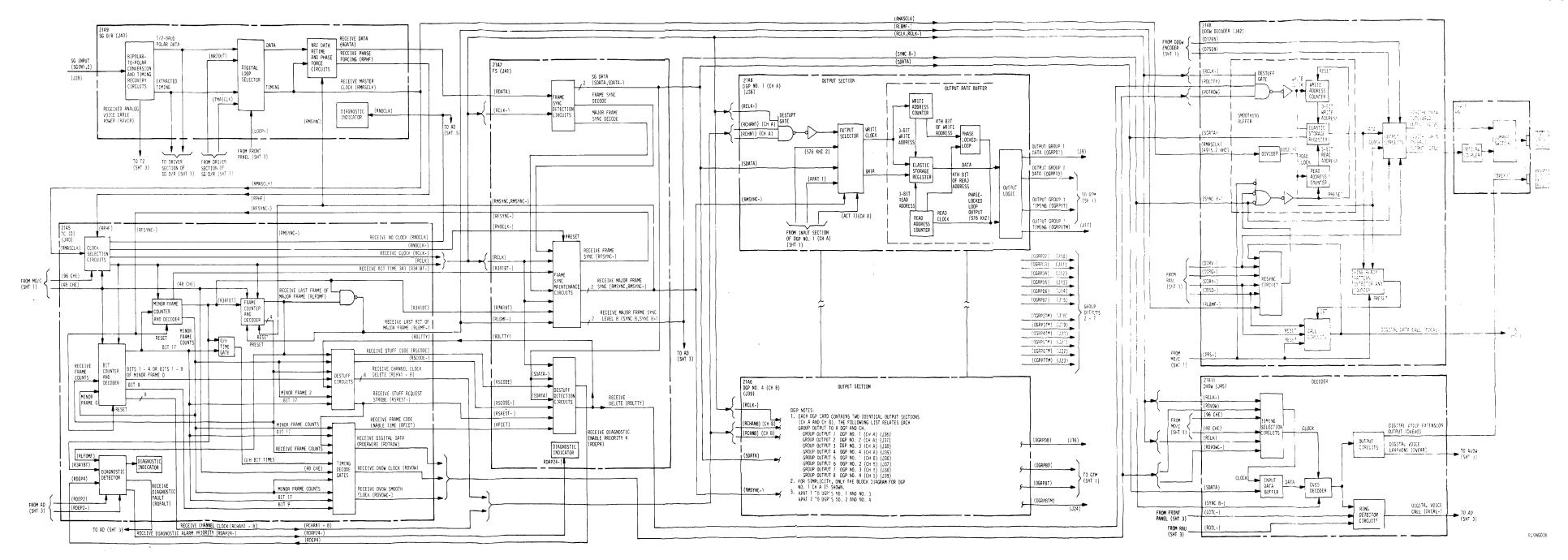

| XII.       | Frame sync (FS) card 21A7                           | 2-44            | 2-82  |

| XIII.      | Group traffic monitor (GTM) card 21A2               | 2-47            | 2-89  |

| XIV.       | Alarm detector(AD) card 21A1                        | 2-50            | 2-94  |

| XV.        | Power generation and distribution                   | 2-53            | 2-102 |

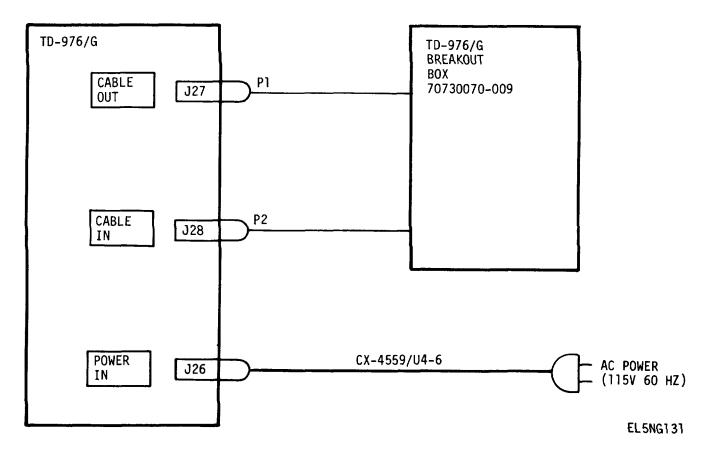

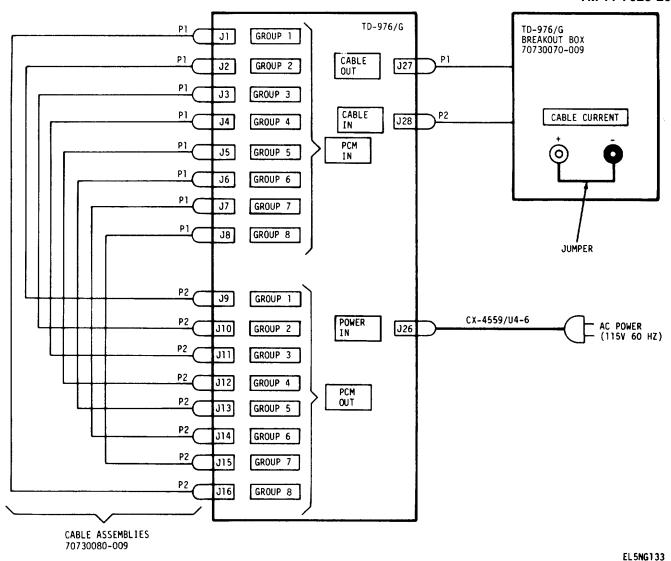

| XVI.       | Cable system power distribution                     | 2-57            | 2-110 |

| XVII.      | Analog voice orderwire (AVOW) card 21A10            | 2-62            | 2-114 |

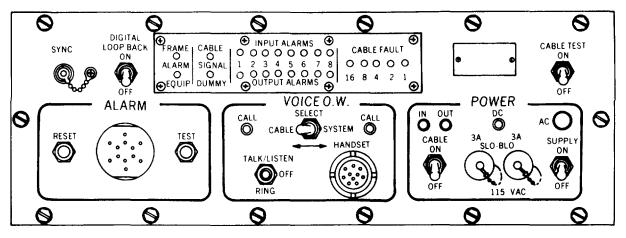

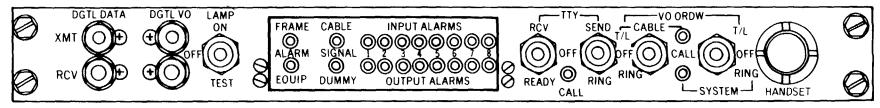

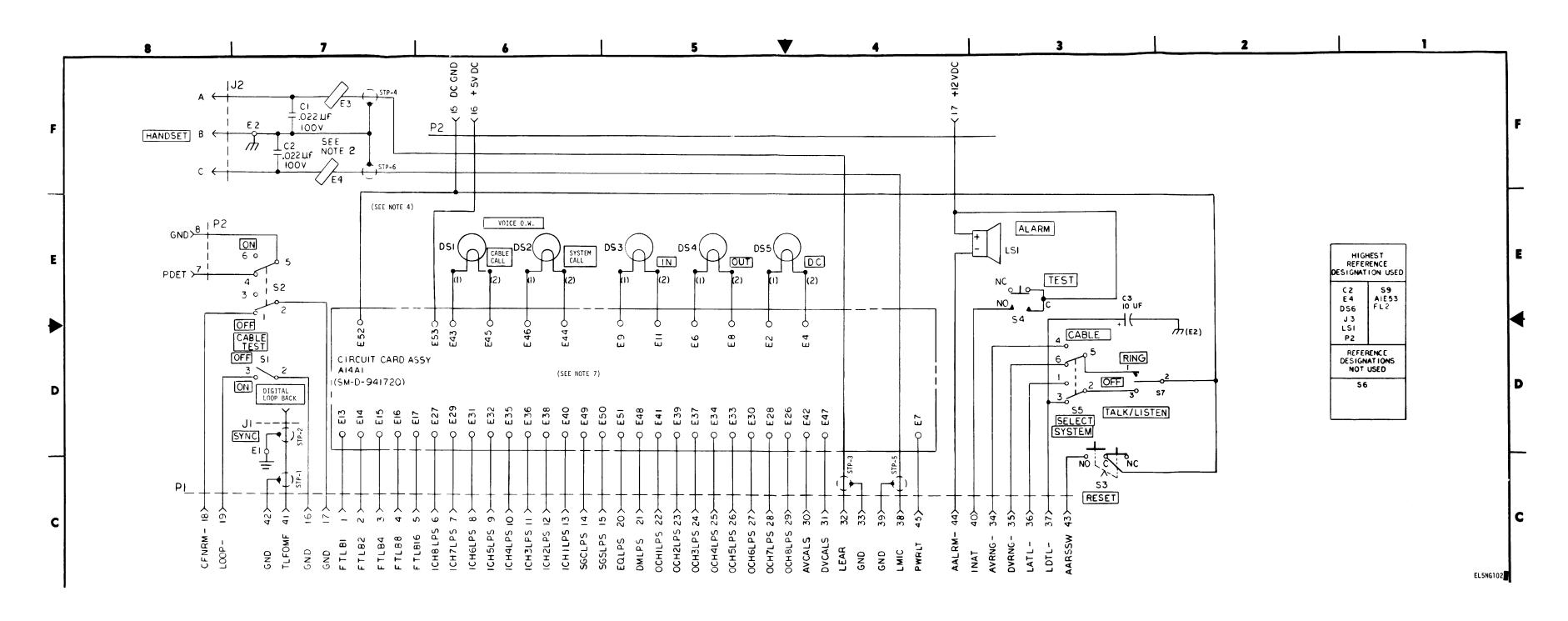

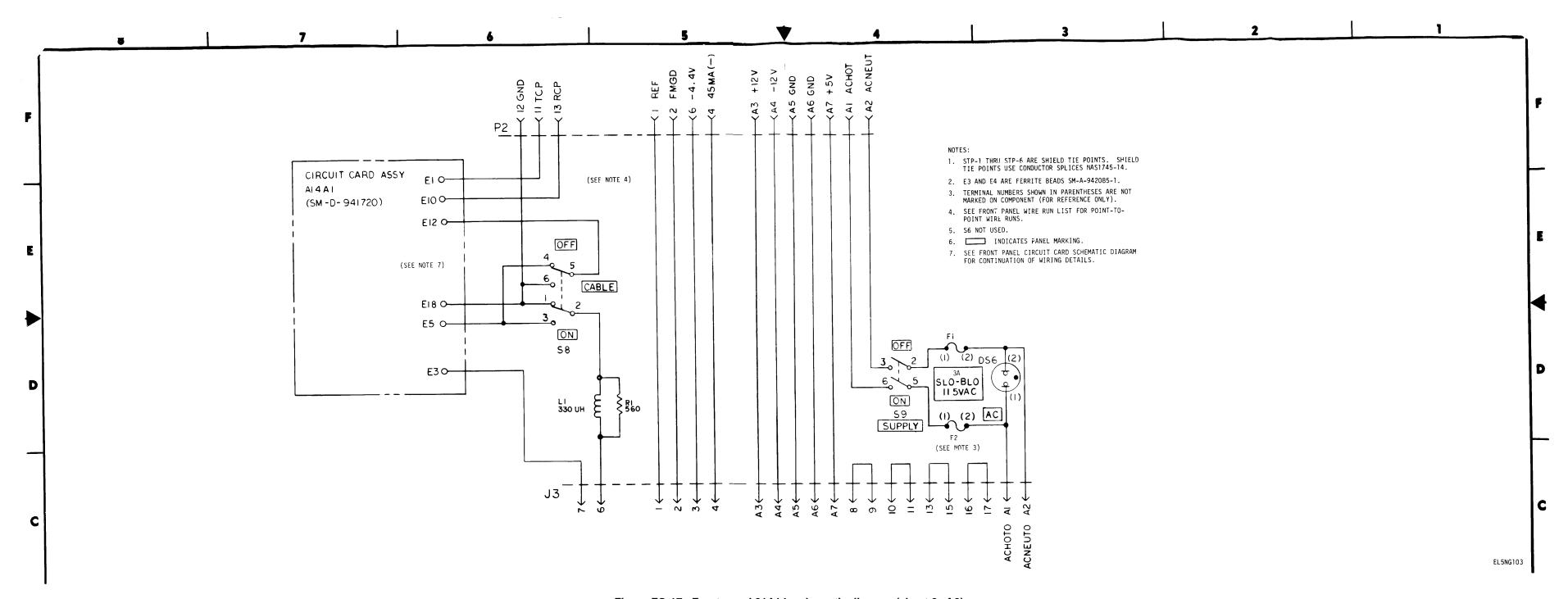

| XVIII.     | Frontpanel21A14                                     | 2-65            | 2-122 |

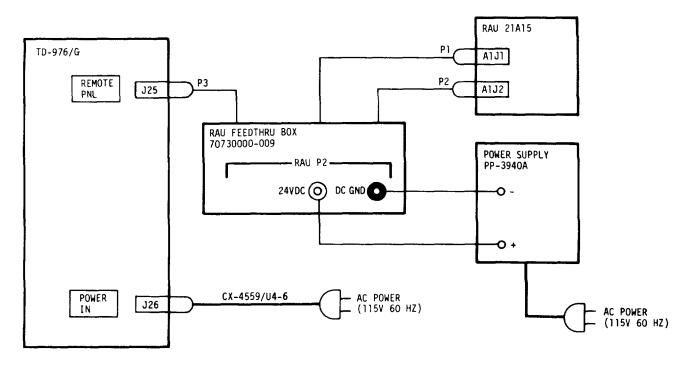

| XIX.       | Remote access unit (RAU)21A15                       | 2-68            | 2-123 |

| CHAPTER 3. | DIRECT SUPPORT MAINTENANCE INSTRUCTIONS             |                 |       |

| Section I. | General                                             | 3-1             | 3-1   |

| II.        | Tools and test equipment                            | 3-4             | 3-2   |

| III.       | TD-976/G inspection and performance test procedures | 3-6             | 3-5   |

| IV.        | TD-9761G troubleshooting procedures                 | 3-16            | 3-30  |

| V.         | Maintenance of MOIC card 21A4                       | 3-24            | 3-40  |

| VI.        | RAU test and troubleshooting procedures             | 3-26            | 3-40  |

| VII.       | Maintenance of RAU 21A15                            | 3-28            | 3-44  |

| VIII.      | Maintenance of front cover, front panel and case    | 3-30            | 3-45  |

| IX.        | Maintenance of card file 21A13                      | 3-36            | 3-61  |

| Χ.         | Printed circuit board repair                        | 3-45            | 3-76  |

| XI.        | Wire run lists                                      | 3-47            | 3-77  |

| CHAPTER 4. | GENERAL SUPPORT MAINTENANCE INSTRUCTIONS            | •               | 0     |

| I.         | General                                             | 4-1             | 4-1   |

| ii.        | Tools and test equipment                            | 4-3             | 4-1   |

| III.       | Power supply inspection and test procedures         | 4-5             | 4-2   |

| IV.        | Power supply troubleshooting procedures             | 4-10            | 4-8   |

| V.         | Maintenance of power supply                         | 4-16            | 4-23  |

| ٧.         | Maintenance of power supply                         | <del></del> -10 | +-23  |

| ADDENIDIY    | A. REFERENCES                                                         | Pag<br>A     |

|--------------|-----------------------------------------------------------------------|--------------|

|              | A. REFERENCES                                                         | Glossary     |

|              |                                                                       | Index        |

|              | LIST OF ILLUSTRATIONS                                                 | iiido        |

| Figure       | Title                                                                 | Pa           |

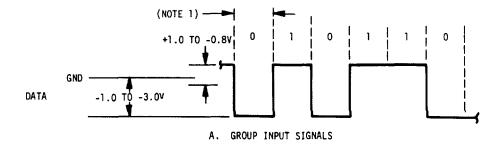

| 2-1          | Group level signals                                                   | 2-2          |

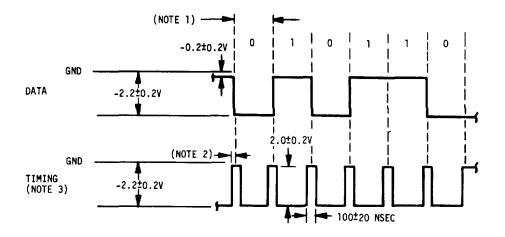

| 2-2          | 112-baud bipolar format (96 channels of data)                         | 2-3          |

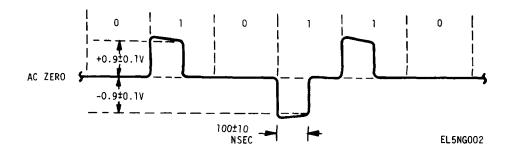

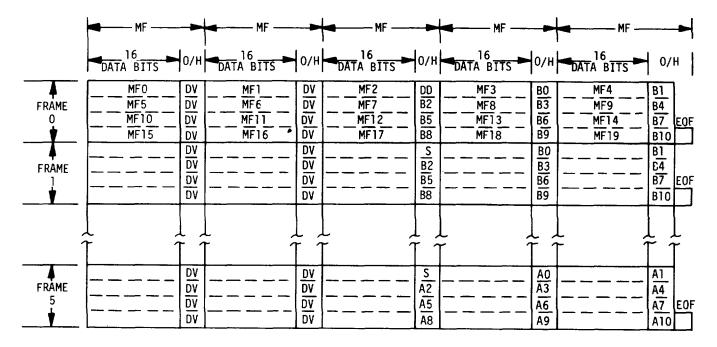

| 2-3          | 96-channel message format                                             | 2-5          |

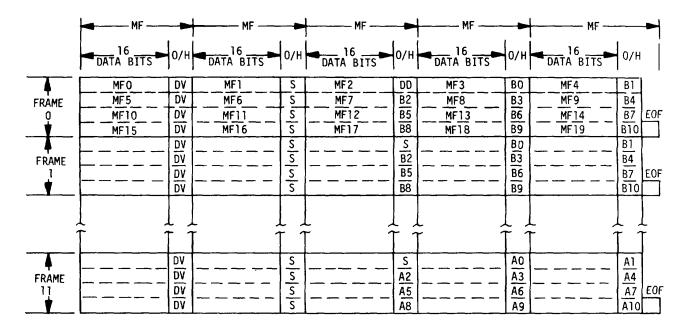

| 2-4          | 48-channel message format                                             | 2-6          |

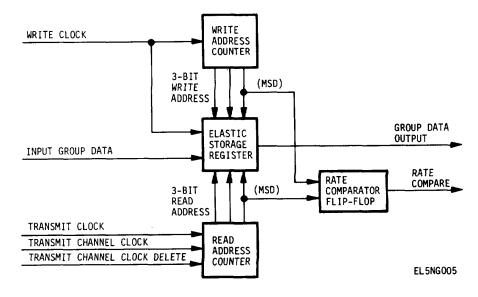

| 2-5          | Input rate buffer, simplified block diagram                           | 2-7          |

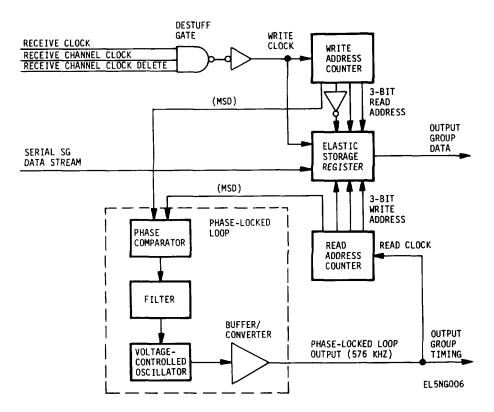

| 2-6          | Output rate buffer, simplified block diagram                          | 2-9          |

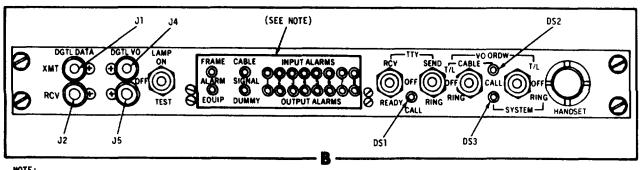

| 2-7          | Front panel 21A14                                                     | 2-1          |

| 2-8          | RAU21A5                                                               | 2-1          |

| 2-9          | MOIC card 21A4, block diagram                                         | 2-2          |

| 2-10         | DGP card 21A6 input section, block diagram                            | 2-4          |

| 2-11         | DGP card 21A6 output section, block diagram                           | 2-4          |

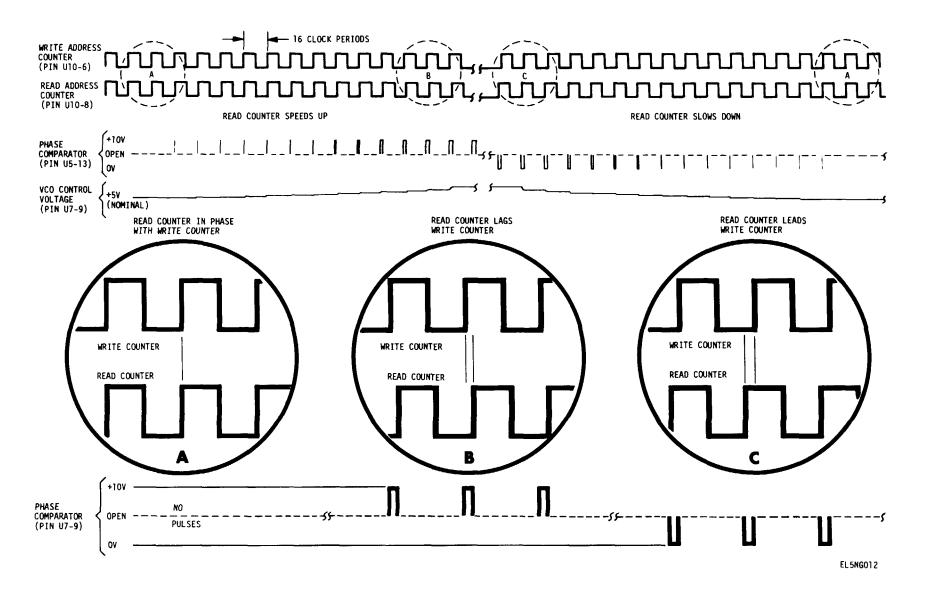

| 2-12         | DGP card 21A6 output section read clock smoothing, typical waveform   | 2-4          |

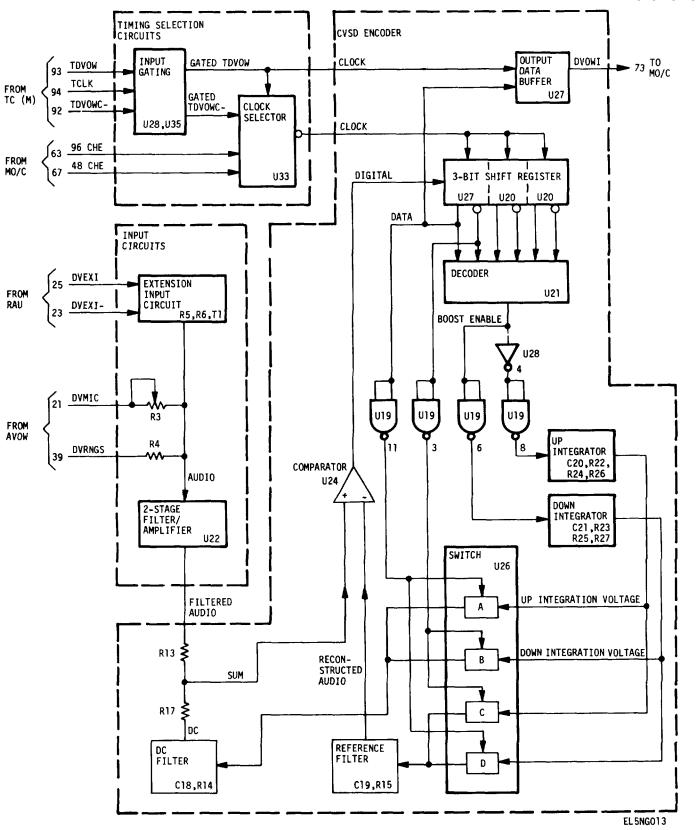

| 2-13         | DVOW card 21All encoder section, block diagram                        | 2-5          |

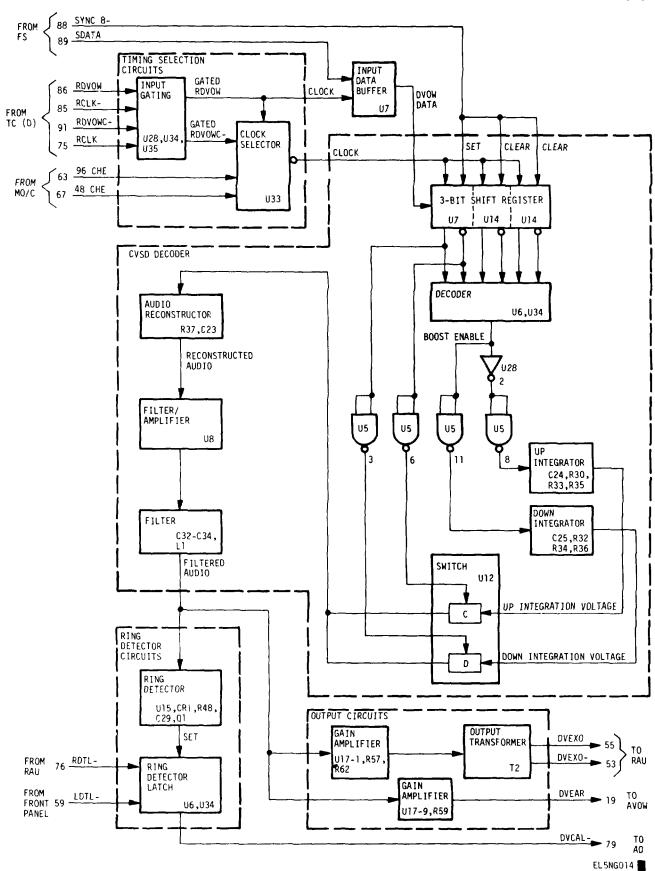

| 2-14         | DVOW card 21A11 decoder section, block diagram                        | 2-5          |

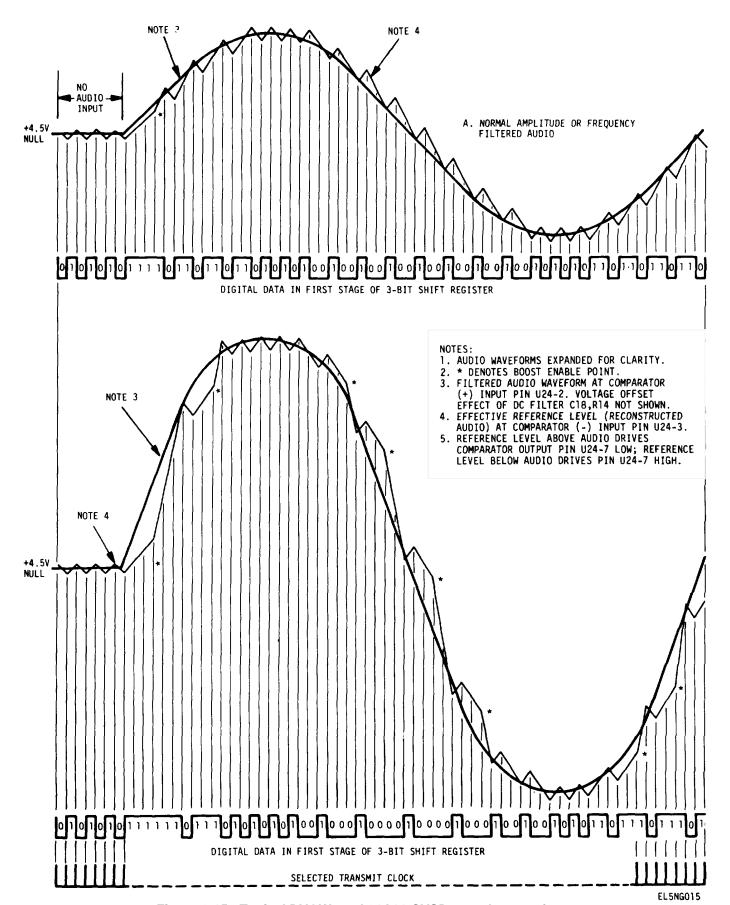

| 2-15         | Typical DVOW card 21A11 CVSD encoder waveforms                        | 2-5          |

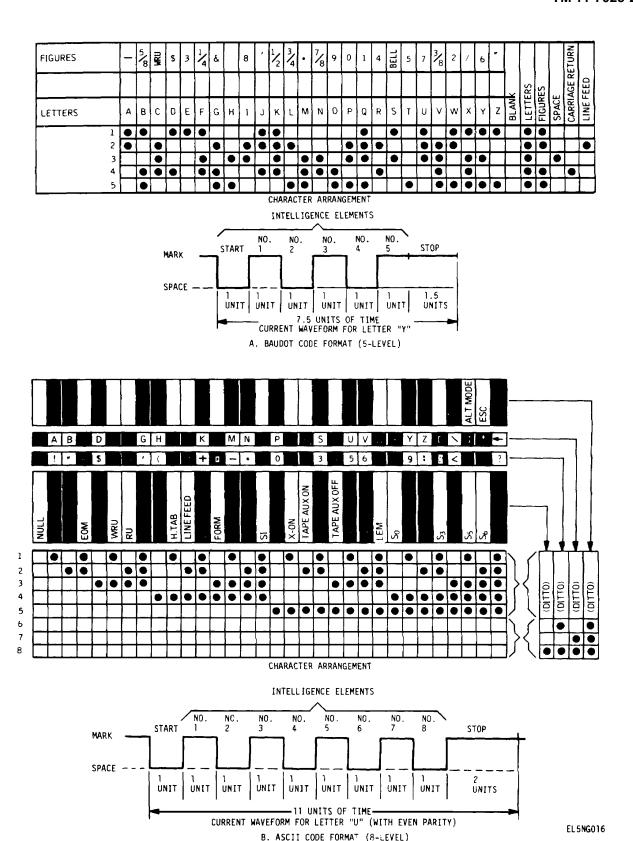

| 2-16         | Baudot and ASCII code formats                                         | 2-6          |

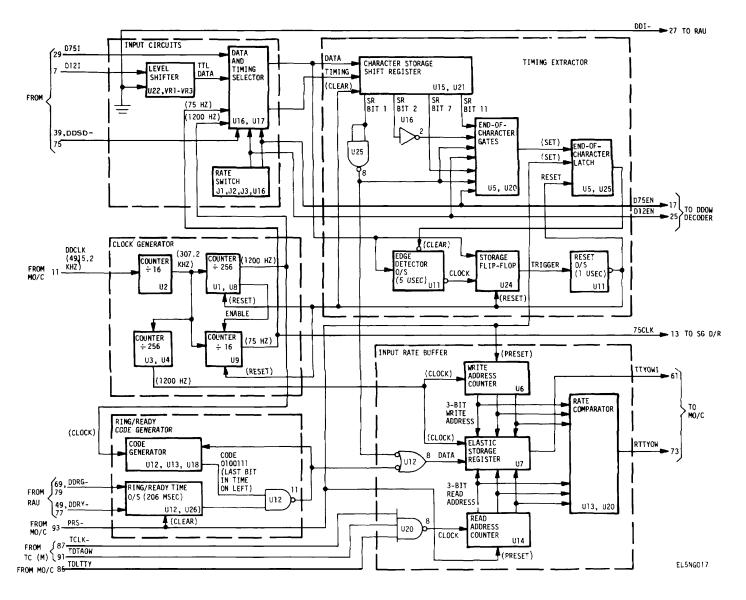

| 2-17         | DDOW encoder card 21A3, block diagram                                 | 2-6          |

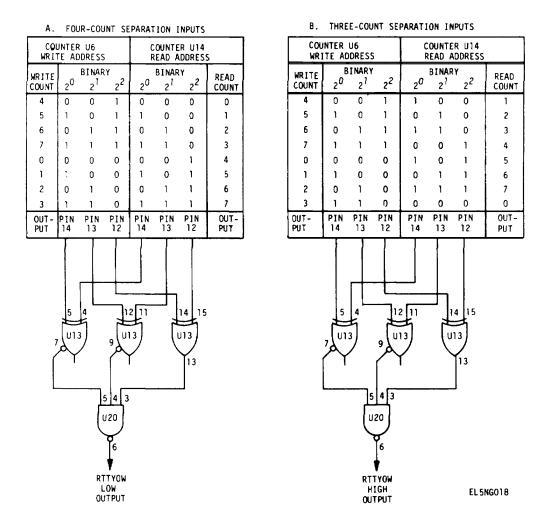

| 2-18         | Rate comparator logic operating conditions                            | 2-7          |

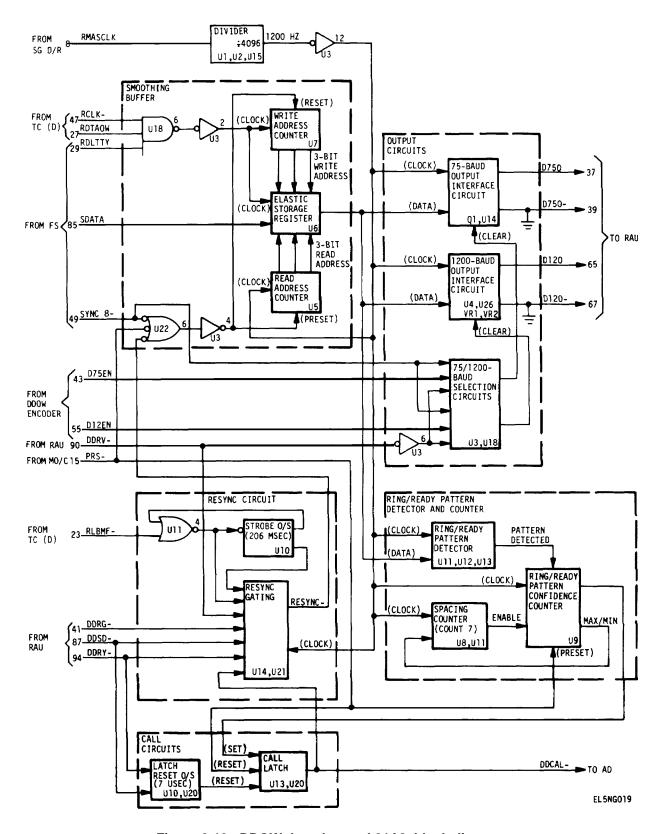

| 2-19         | DDOW decoder card 21A8, block diagram                                 | 2-7          |

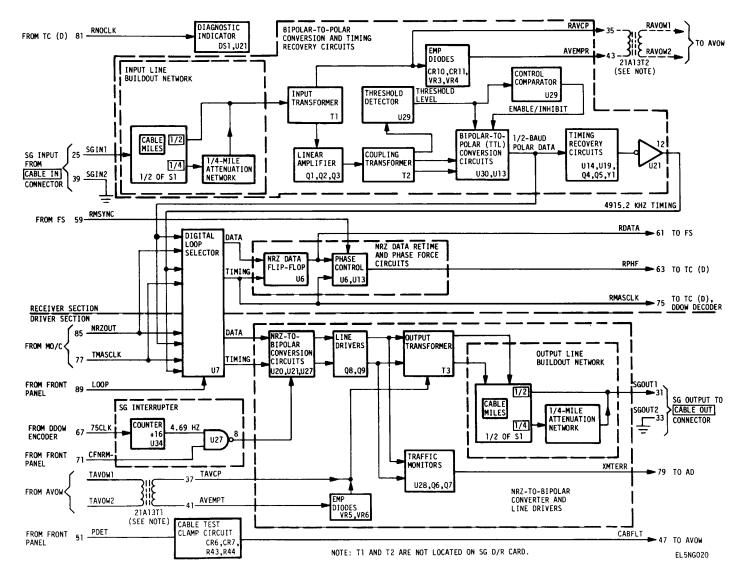

| 2-20         | SG DIR card 21A9, block diagram                                       | 2-7          |

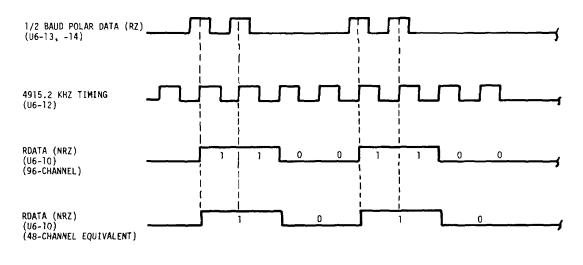

| 2-21         | RZ-to-NRZ conversion waveform diagram                                 | 2-8          |

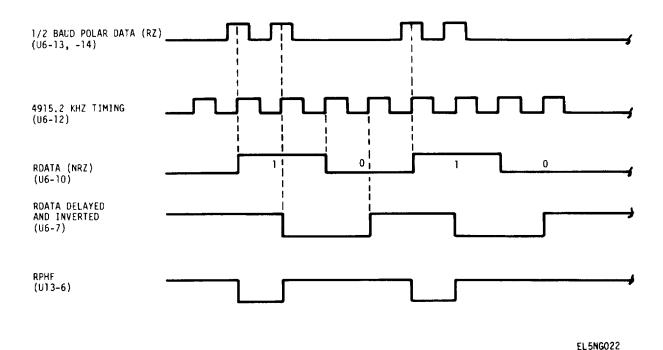

| 2-22         | Phase control circuit RPHF waveform diagram                           | 2-8          |

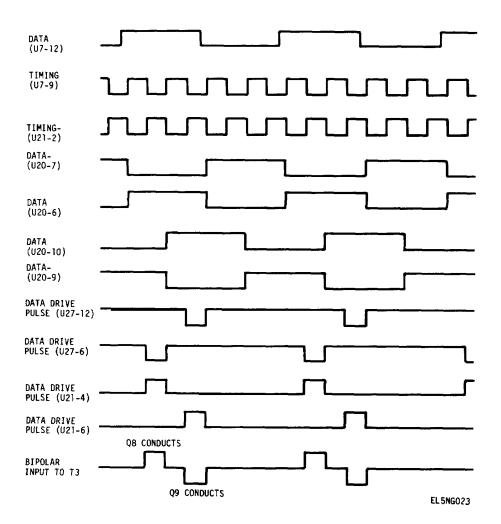

| 2-23         | NRZ-to-bipolar conversion waveform diagram                            | 2-8          |

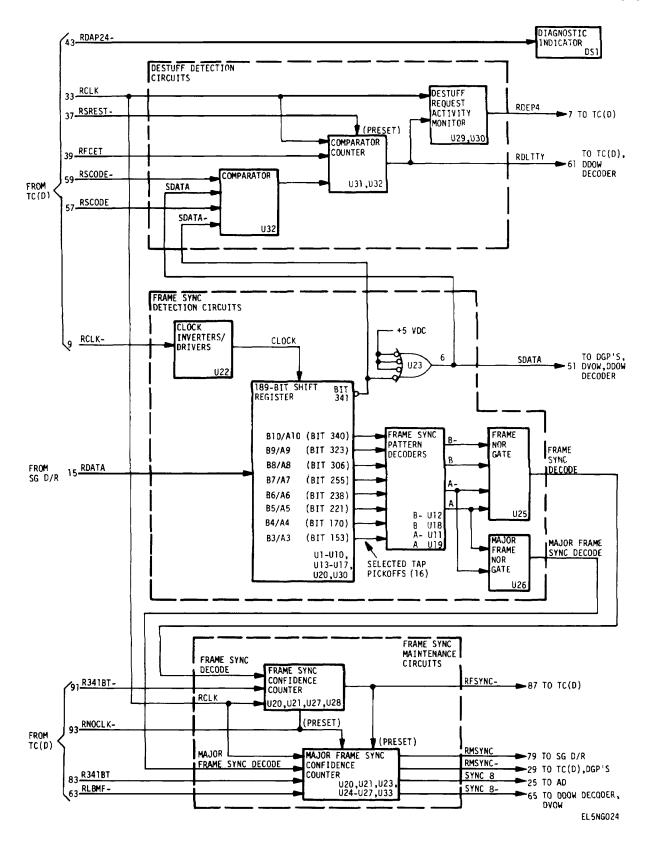

| 2-24         | FS card 21A7, block diagram                                           | 2-8          |

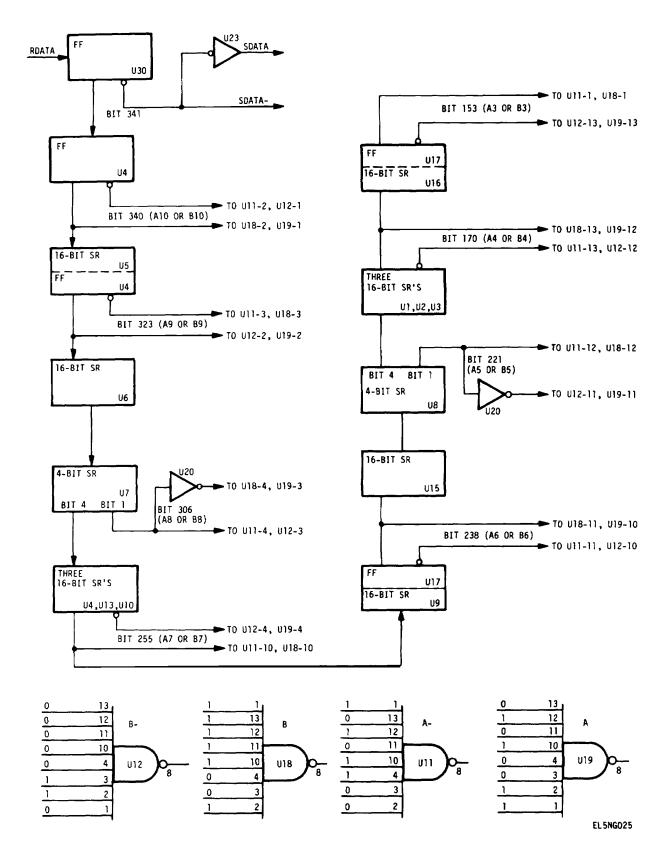

| 2-25         | 189-bit shift register and pattern decode gates, simplified diagram   | 2-8          |

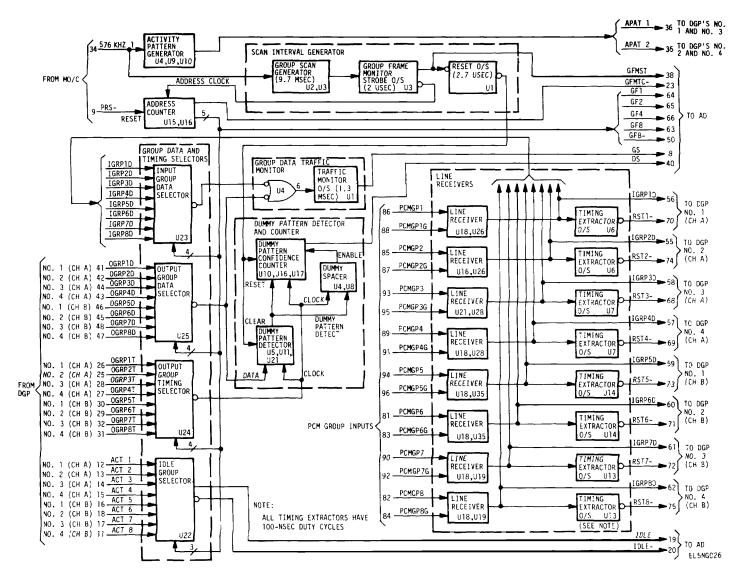

| 2-26         | GTM card 21A2, block diagram                                          | 2-9          |

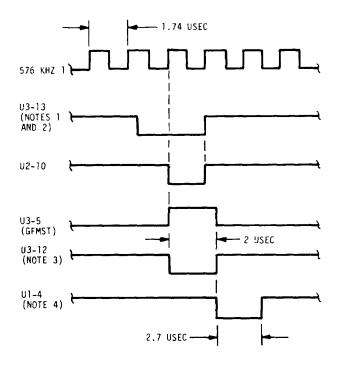

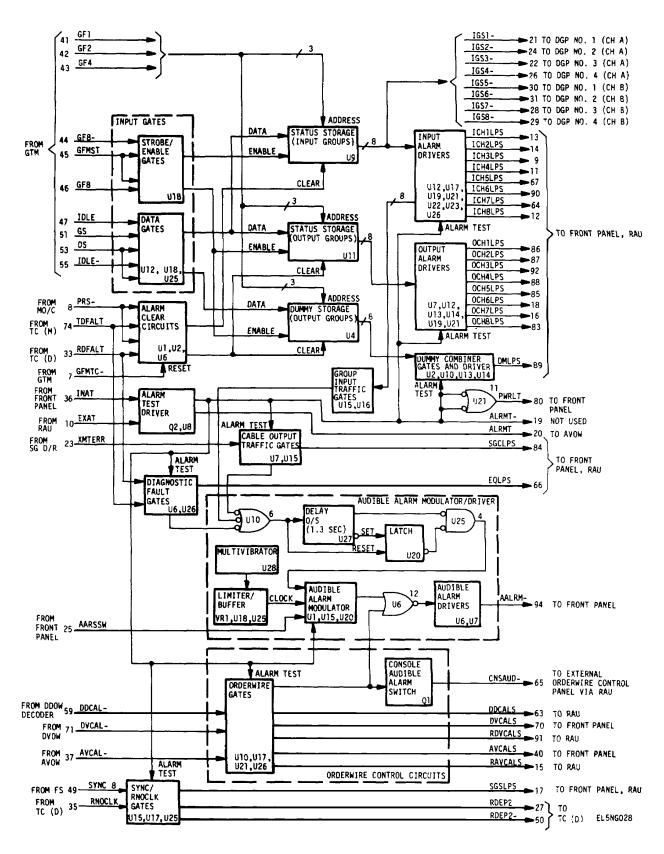

| 2-27<br>2-28 | Scan interval generator timing diagramAD card 2 A1, block diagram     | 2-9:<br>2-9: |

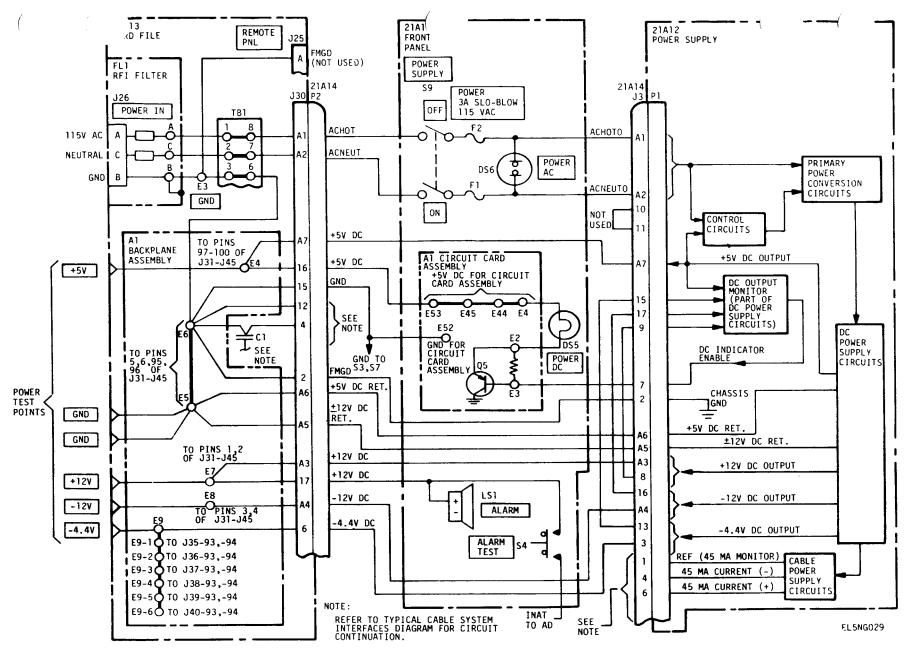

| 2-20<br>2-29 | Overall power generation and distribution diagram                     | 2-9          |

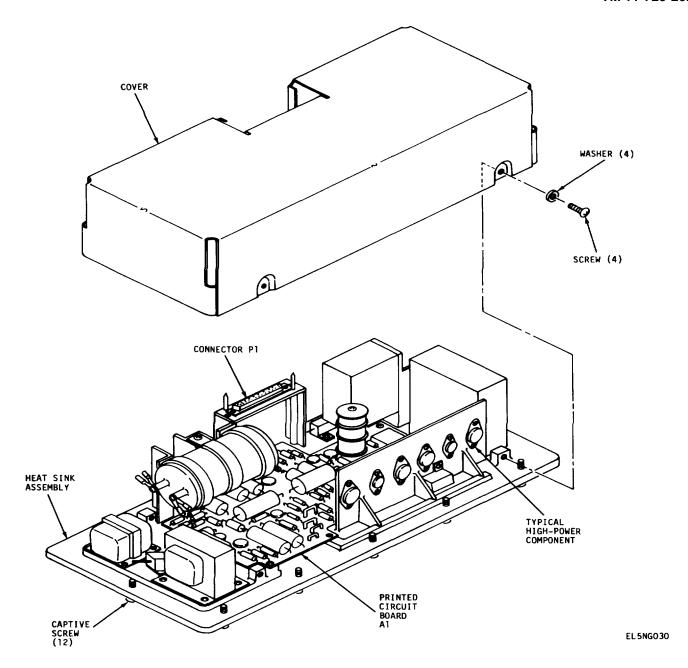

| 2-29         | Power supply 21A12, major component location diagram                  | 2-10         |

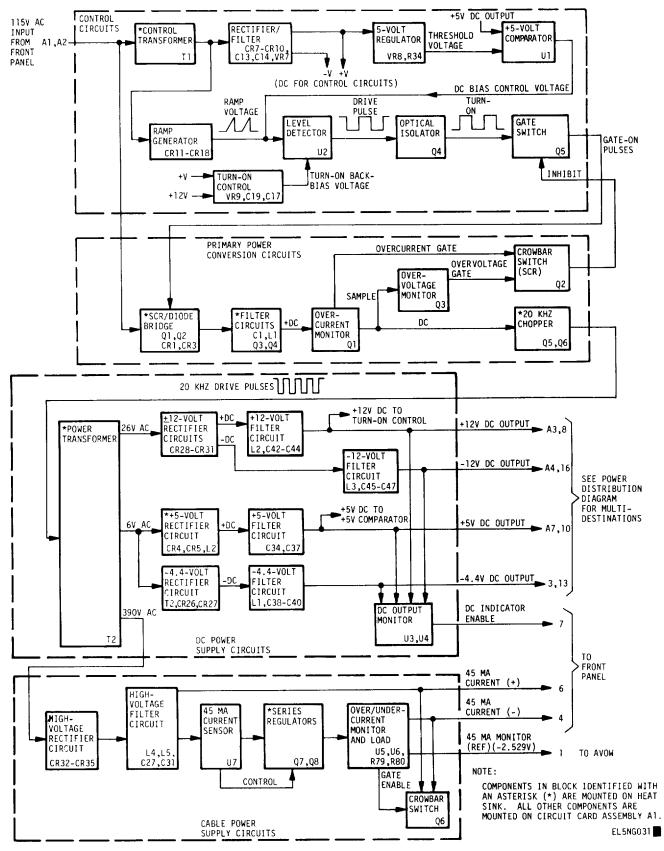

| 2-30<br>2-31 | Power supply 21A12, block diagram                                     | 2-1          |

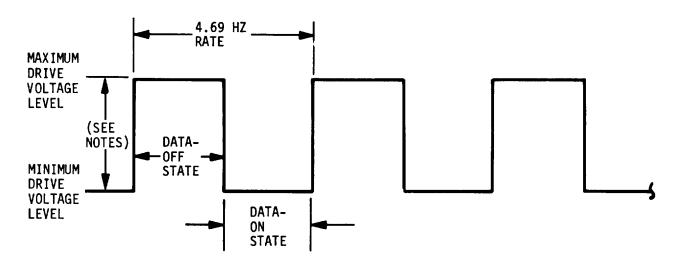

| 2-32         | CABFLT signal waveform diagram                                        | 2-1          |

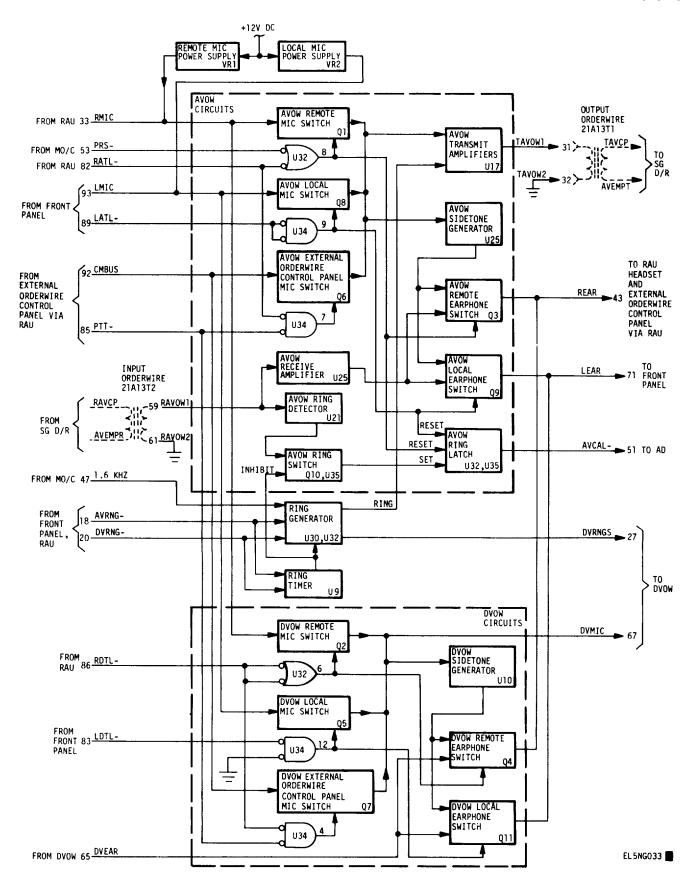

| 2-33         | AVOW card 21A10 voice orderwire circuits, block diagram               | 2-1          |

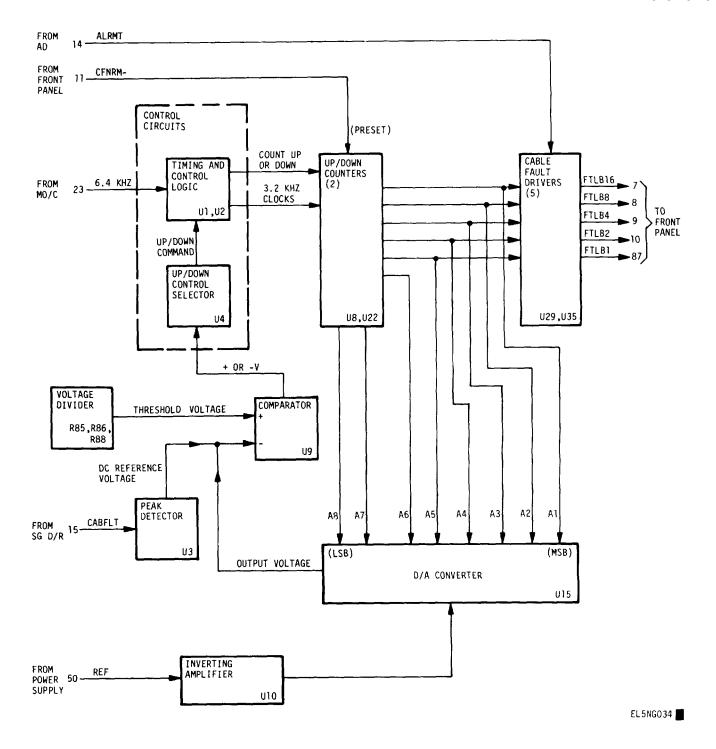

| 2-34         | AVOW card 21A10 cable fault circuits, block diagram                   | 2-1          |

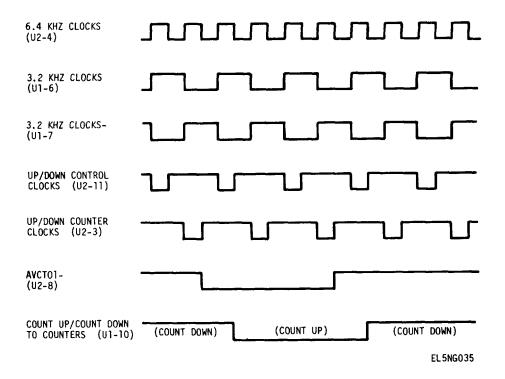

| 2-35         | Up/Down count control waveform diagram                                | 2-1:         |

| 2-36         | TTY data 75-baud interface circuit, simplified schematic diagram      | 2-1          |

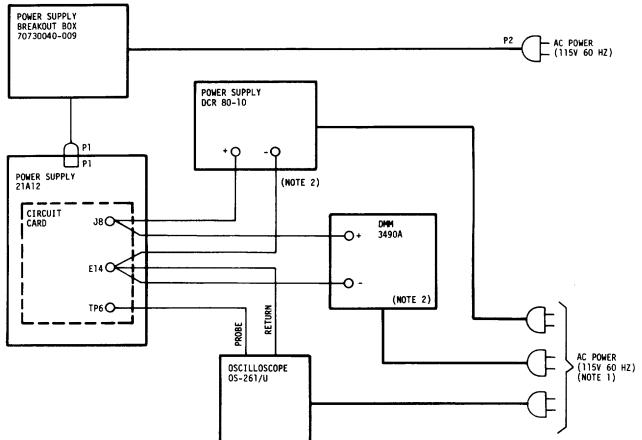

| 3-1          | Power supply output test and cable fault detection test setup diagram | 3-1          |

| 3-2          | Alarm and indicator lamp test setup diagram                           | 3-1          |

| 3-3          | Data transfer test setup diagram                                      | 3-1          |

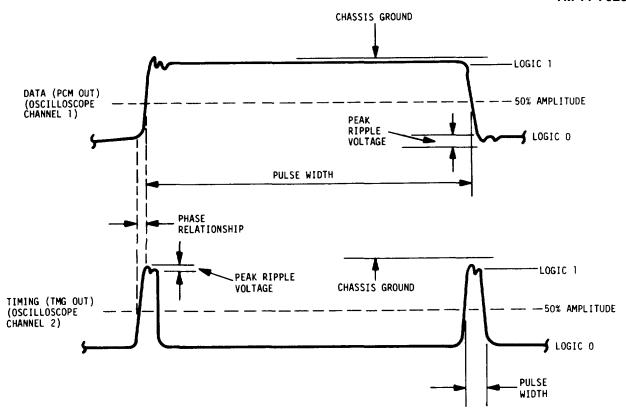

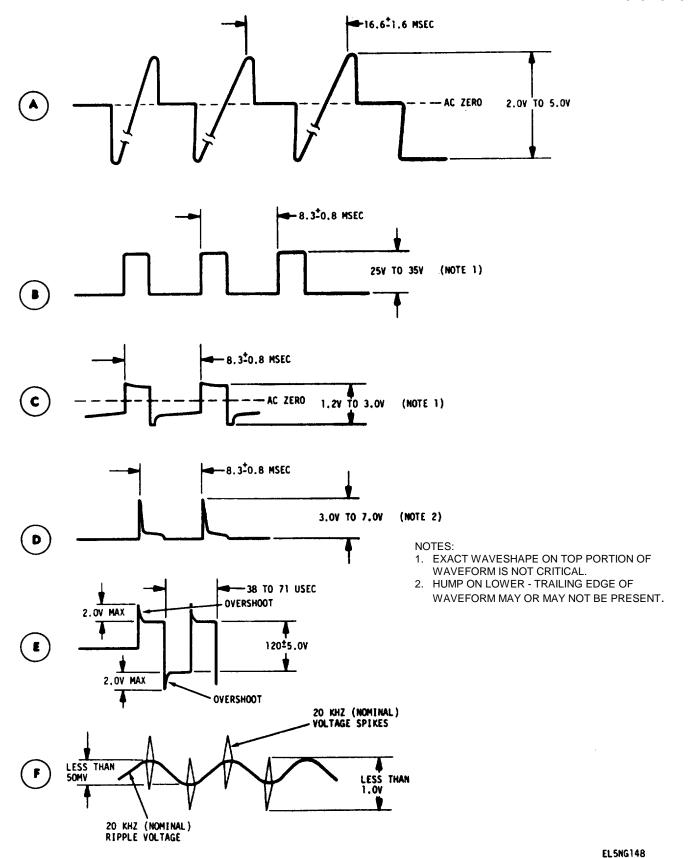

| 3-4          | PCM data and timing waveforms                                         | 3-1          |

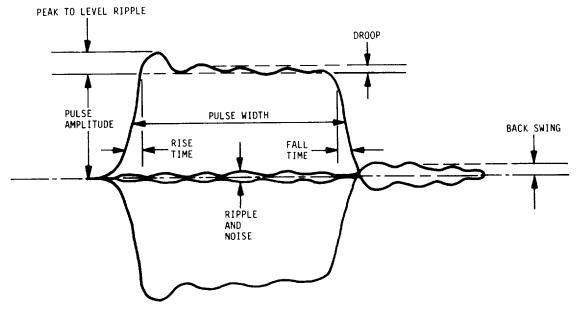

| 3-5          | SG output data characteristics                                        | 3-1          |

| 3-6          | AVOW test setup diagram                                               | 3-2          |

| 3-7          | DVOW teat setup diagram                                               | 3-2          |

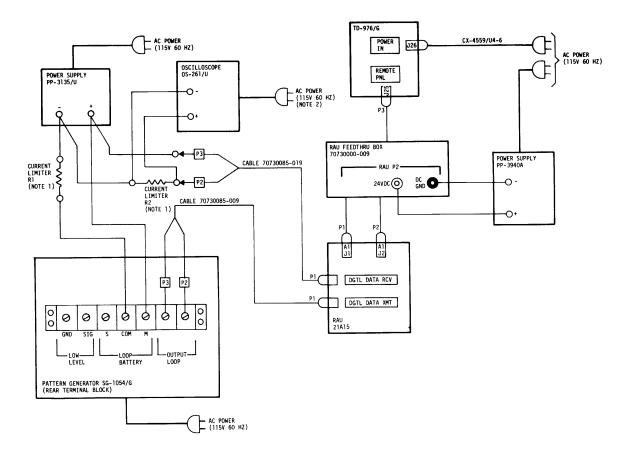

| 3-8          | DDOW test setup diagram                                               | 3-2          |

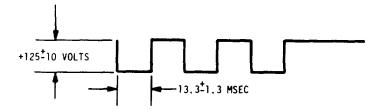

| 3-9          | DDOW waveforms                                                        | 3-3          |

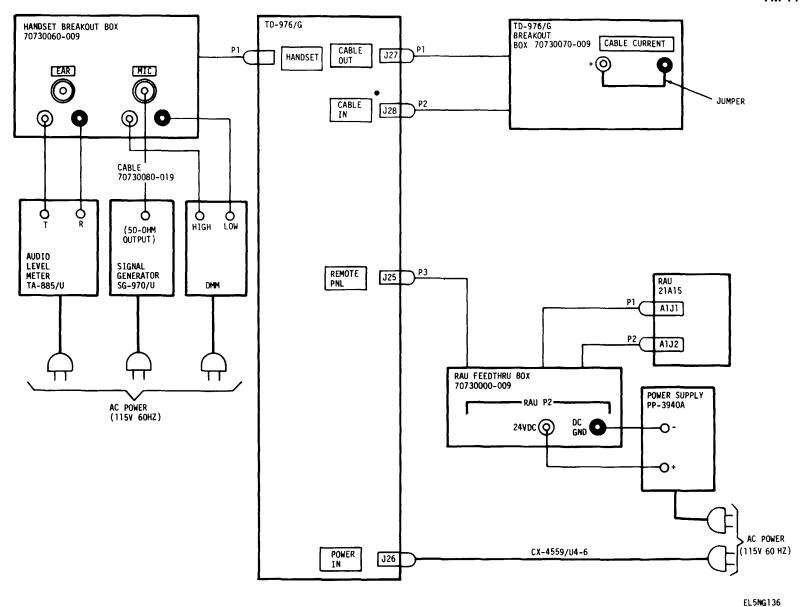

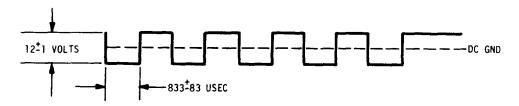

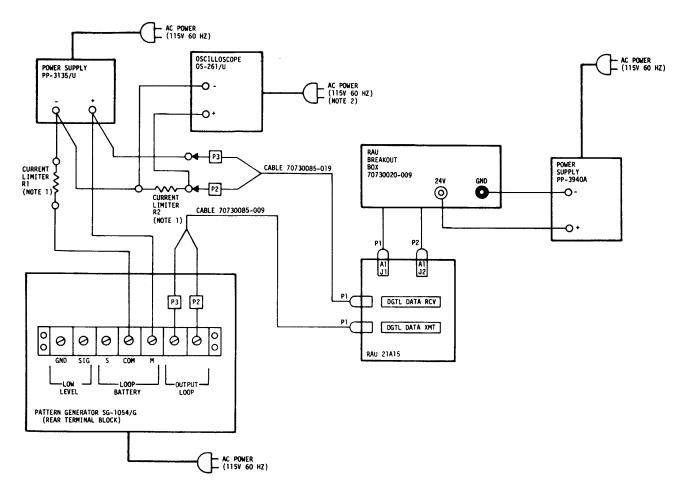

| 3-10         | RAU indicator, switch, and continuity test setup                      | 3-4          |

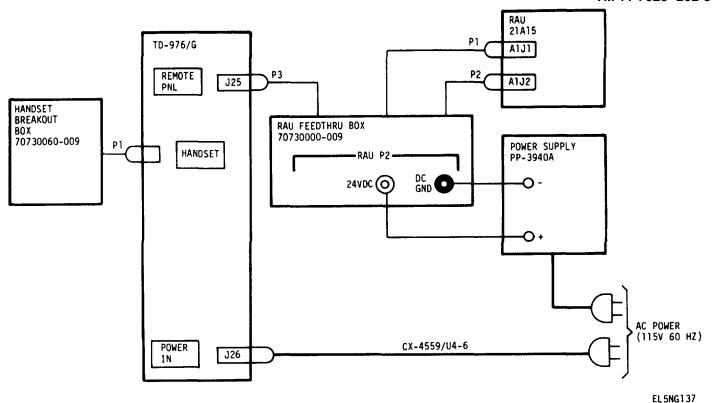

| 3-11         | 75-baud digital data check test setup                                 | 3-4          |

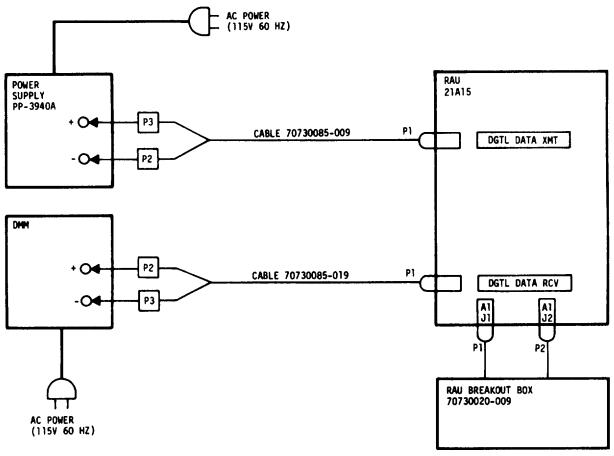

| 3-12         | 1200-baud loop test setup                                             | 3-4          |

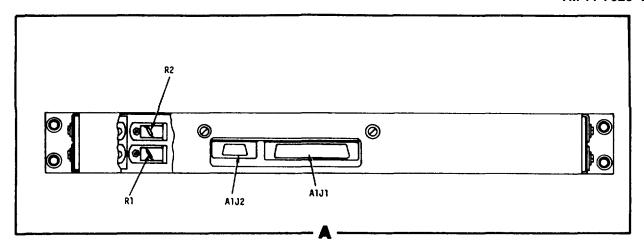

| 3-13         | RAU 21A15, component location diagram                                 | 3-4          |

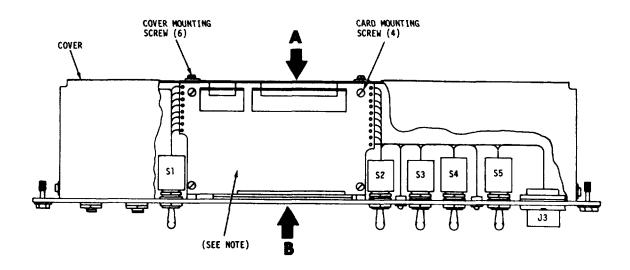

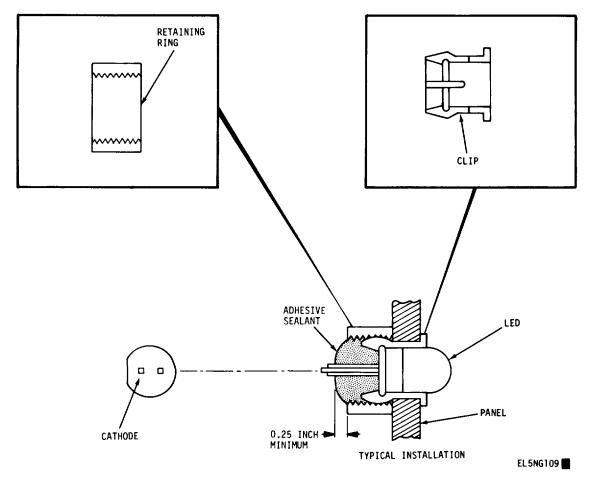

| 3-14         | RAU 21A15, DS1, D82, and DS3 installation diagram                     | 3-4          |

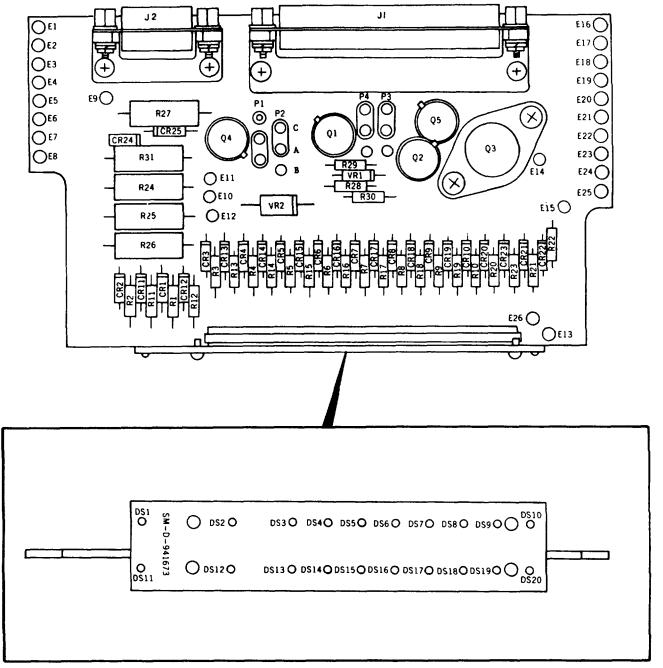

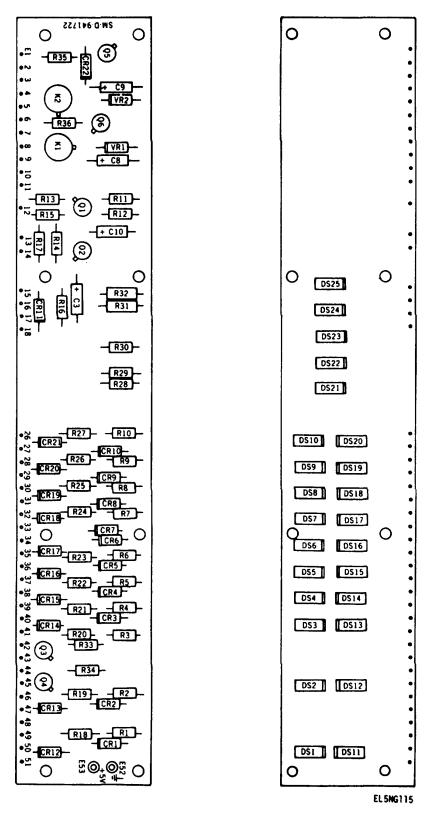

| 3-15         | RAU circuit card 21A15A1, component location diagram                  | 3-5          |

| 3-16         | Front cover, retaining pad installation diagram                       | 3-5          |

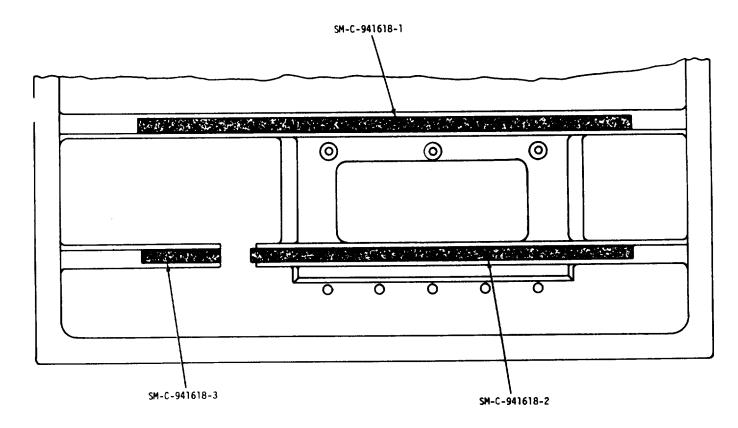

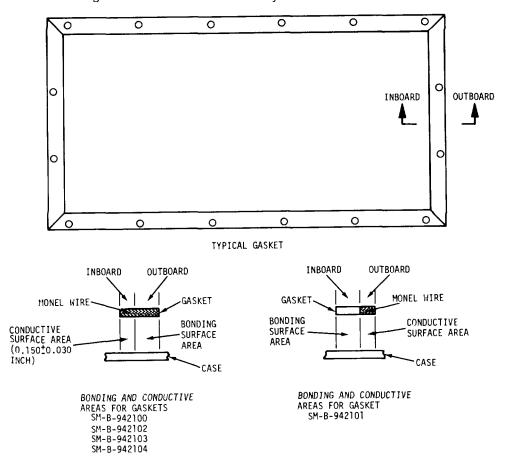

| 3-17         | Front cover, gasket installation diagram                              | 3-5          |

| 3-18         | Front panel 21A4, removal and installation diagram                    | 3-5          |

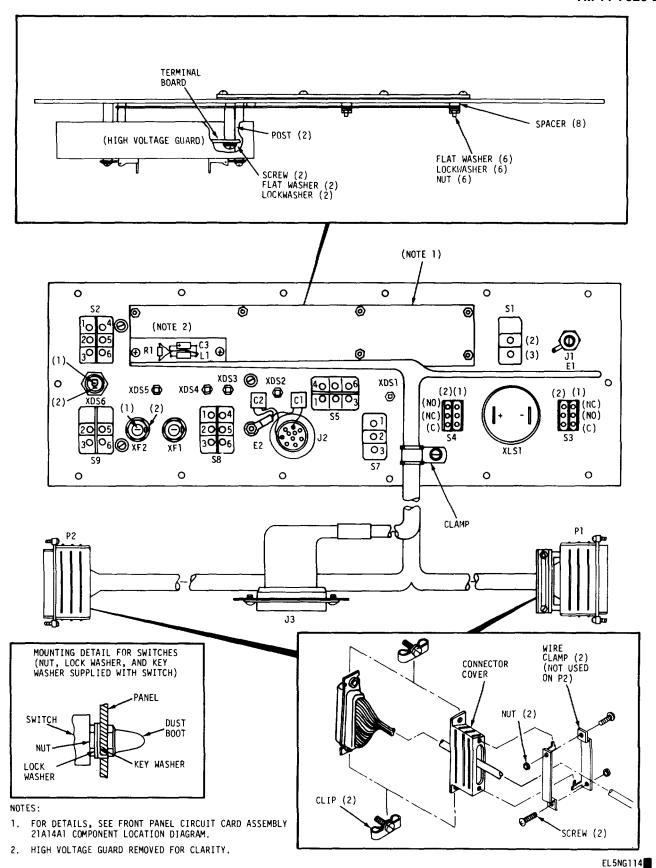

| 3-19         | Front panel 21A14, component location diagram                         | 3-5          |

| 3-20         | Front panel circuit card 21A14A1, component location diagram          | 3-5          |

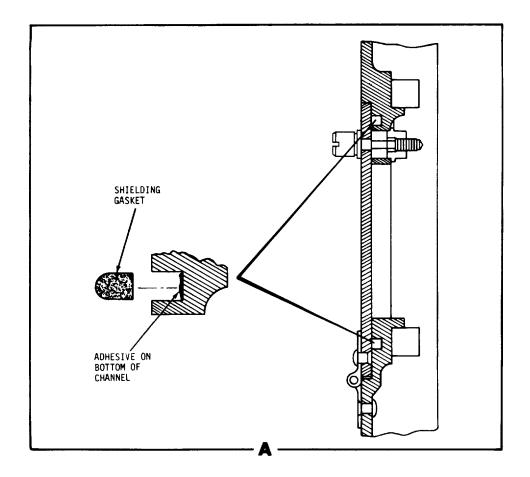

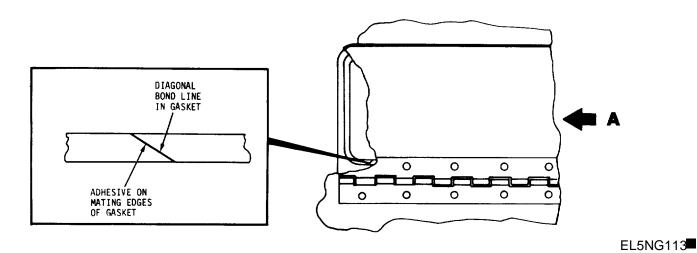

| 3-21         | Typical shielding gasket installation diagram                         | 3-5          |

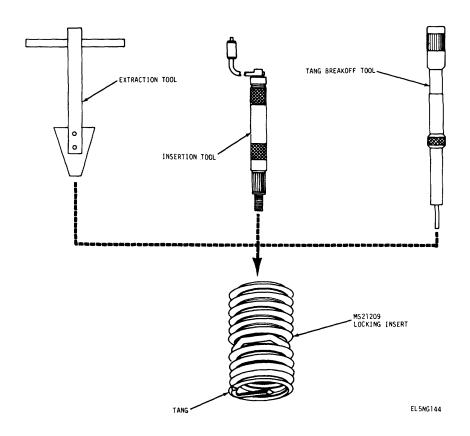

| 3-22         | Typical locking insert and extraction/insertion tools                 | 3-6          |

# TM 11-7025-202-34

| Figure           | Title                                                                                 | Page        |

|------------------|---------------------------------------------------------------------------------------|-------------|

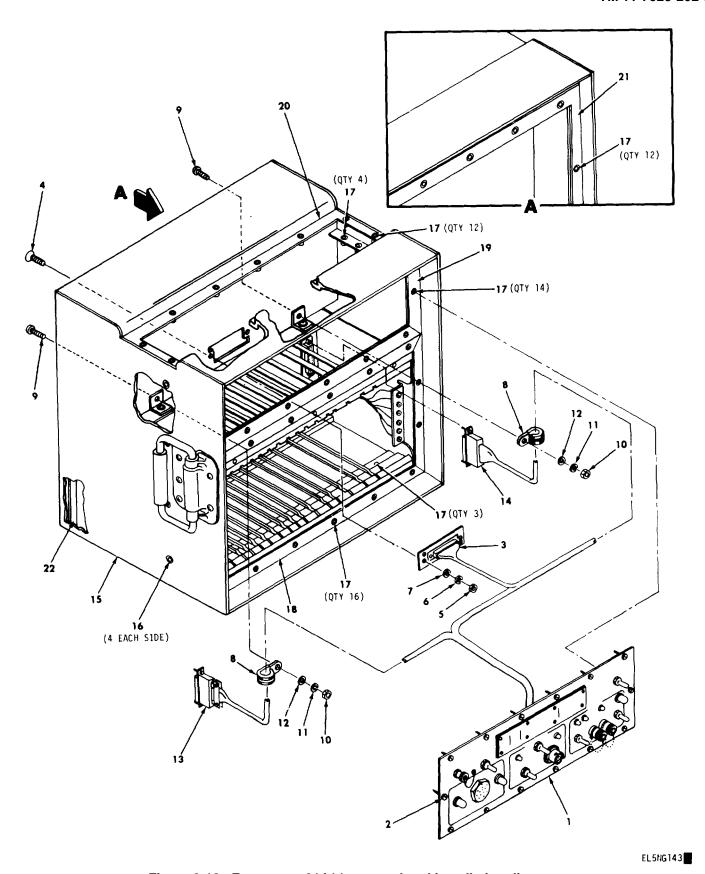

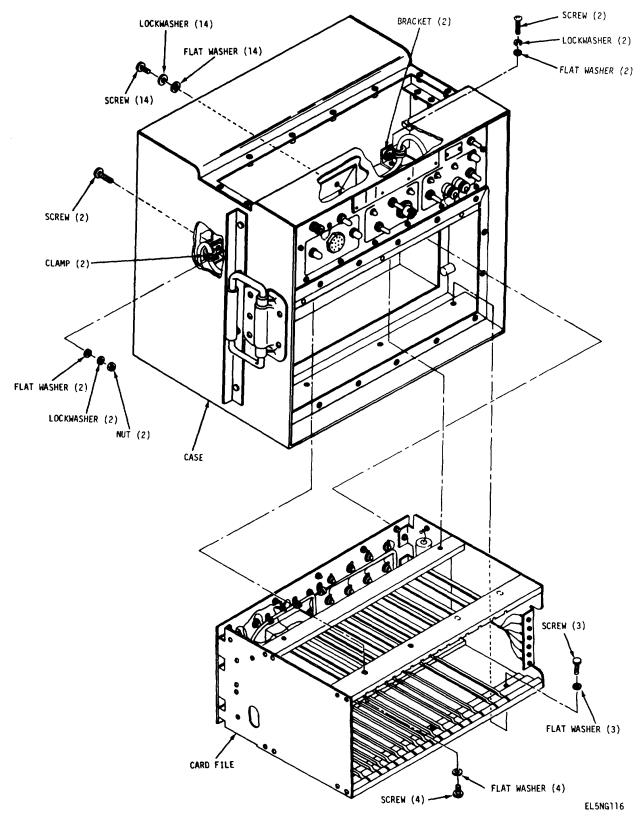

| 3-23             | Card file 21A13, removal and installation diagram                                     | 3-63        |

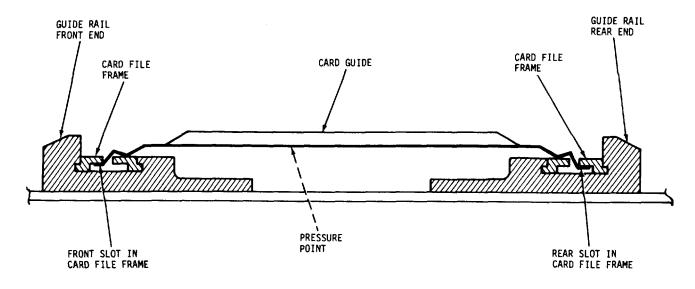

| 3-24             | Card guide, removal and installation diagram                                          |             |

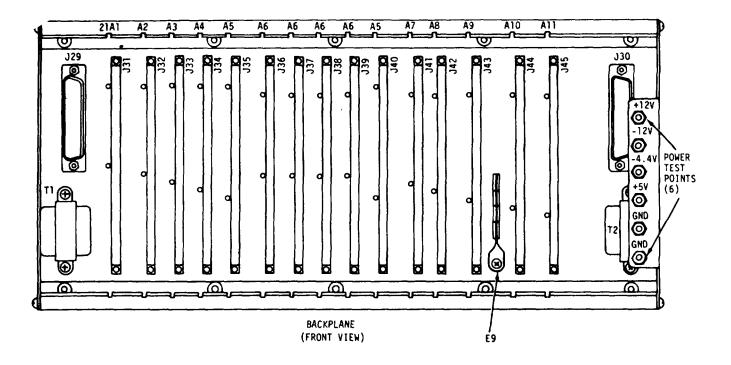

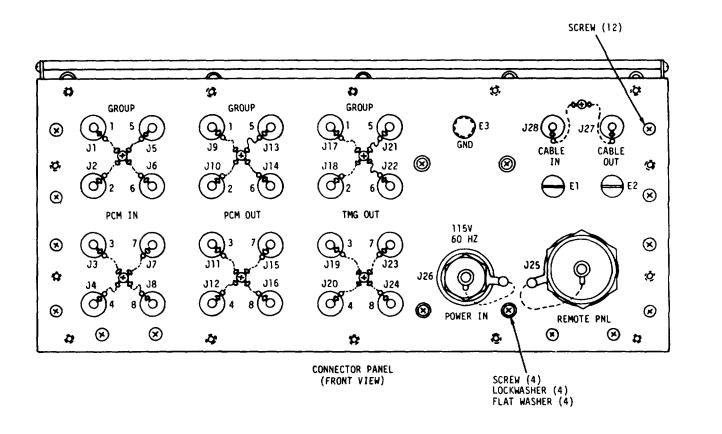

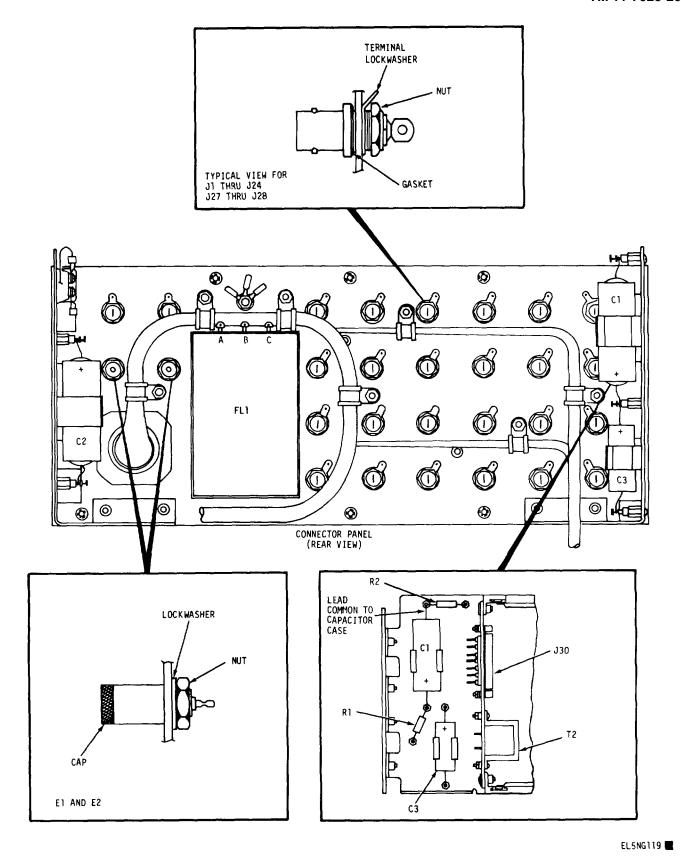

| 3-25             | Card file 21A13, component location diagram (3 sheets)                                | 3-65, 3-66, |

|                  |                                                                                       | 3-67        |

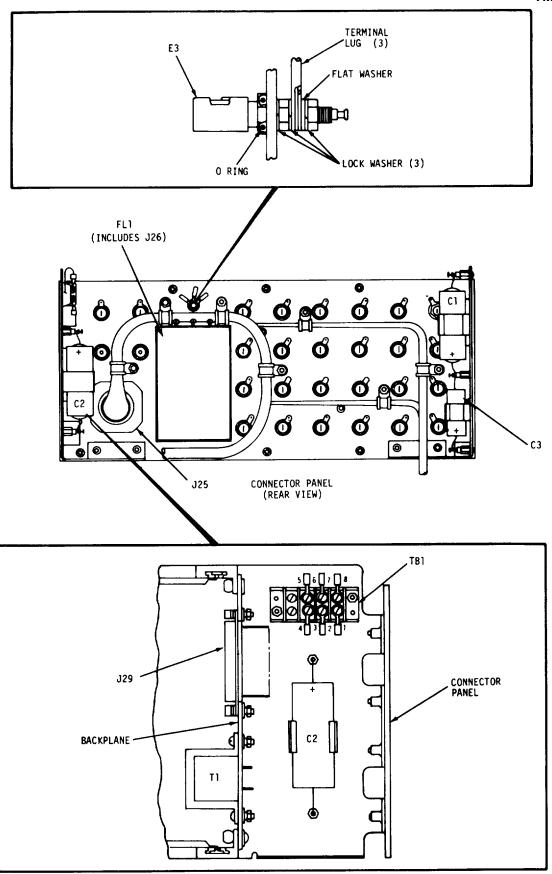

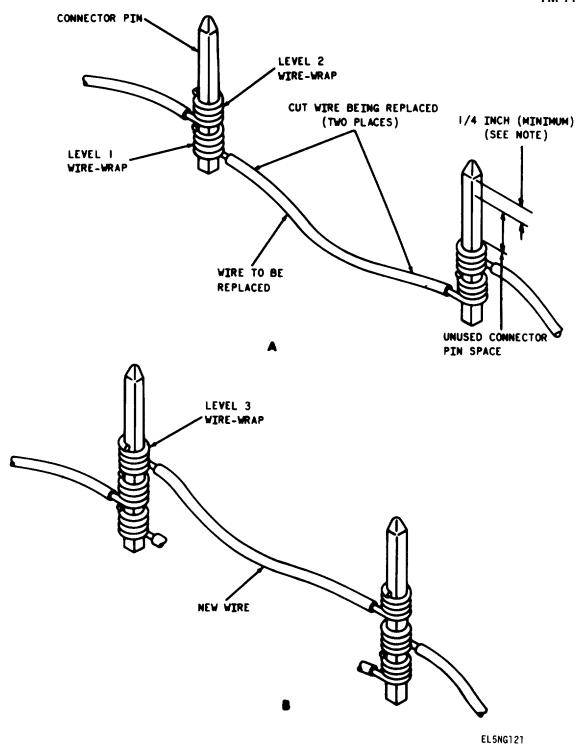

| 3-26             | Backplane, wire replacement diagram                                                   | 3-68        |

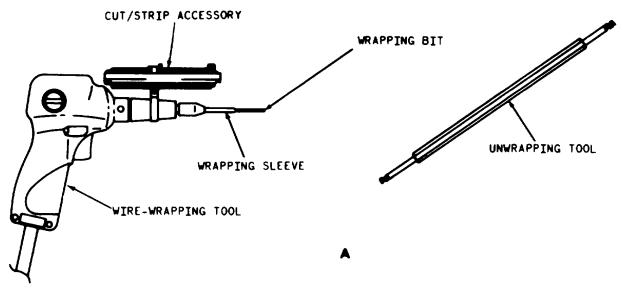

| 3-27             | Wire-wrapping tools and simplified wire installation diagram                          | 3-70        |

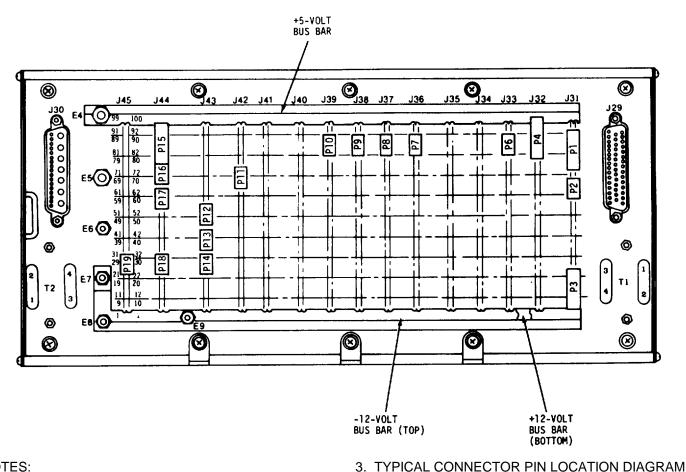

| 3-28             | Backplane, connector pin location diagram                                             |             |

| 3-29             | Backplane, connector pin installation diagram                                         | 3-73        |

| 3-30             | Typical interface connector, component location diagram                               | 3-74        |

| 3-31             | TD-976/G, simplified overall wiring diagram                                           | 3-80        |

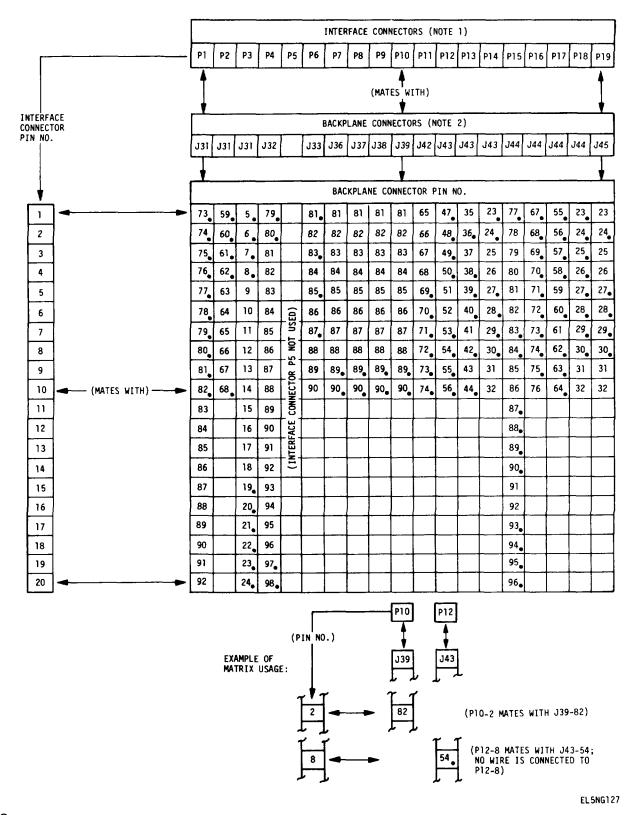

| 3-32             | Interface connector-to-back-plane connector wiring diagram matrix                     | 3-81        |

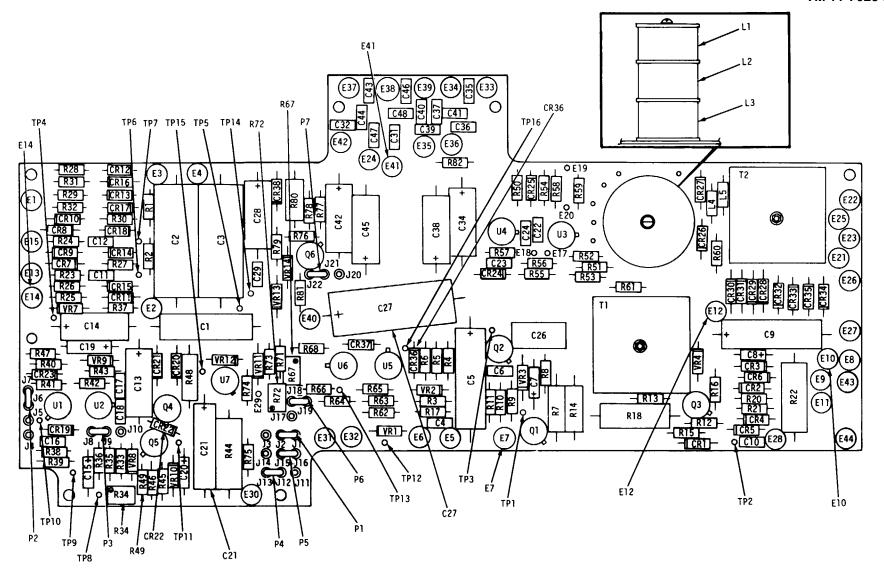

| 4-1              | Circuit card 21A12A1 components location diagram                                      | 4-5         |

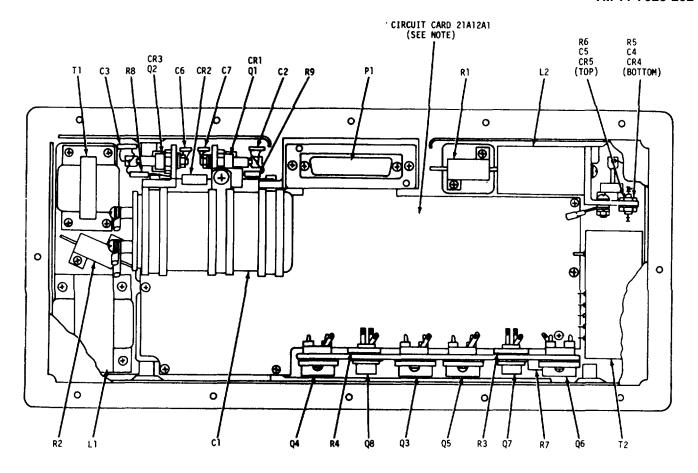

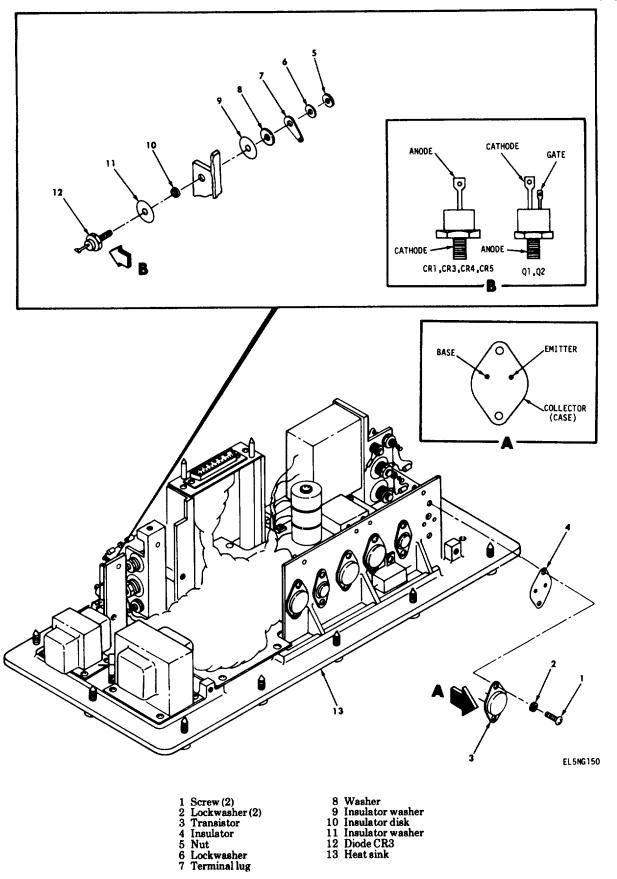

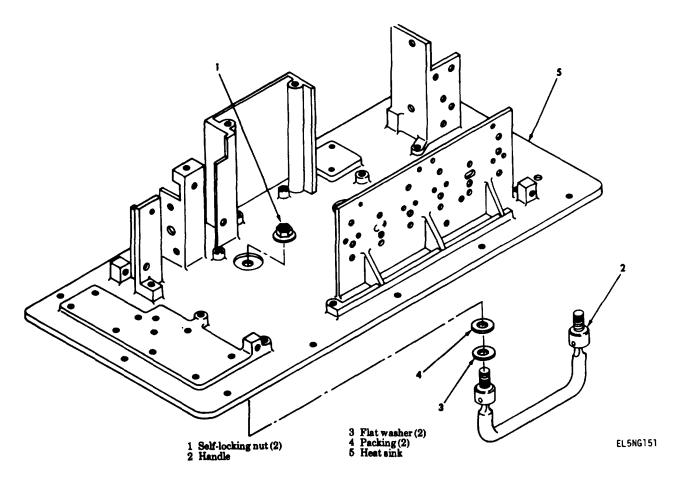

| 4-2              | Heat sink components location diagram                                                 | 4-6         |

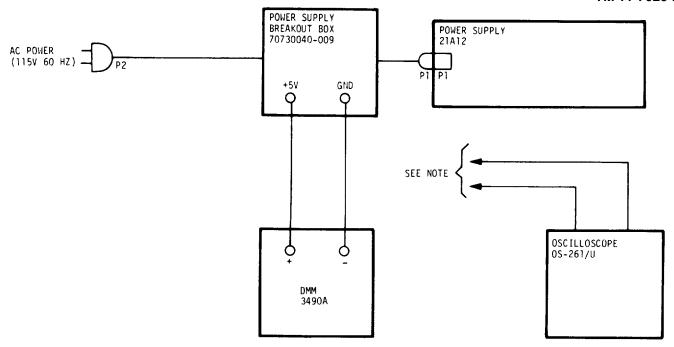

| 4-3              | Power supply test setup diagram                                                       | 4-9         |

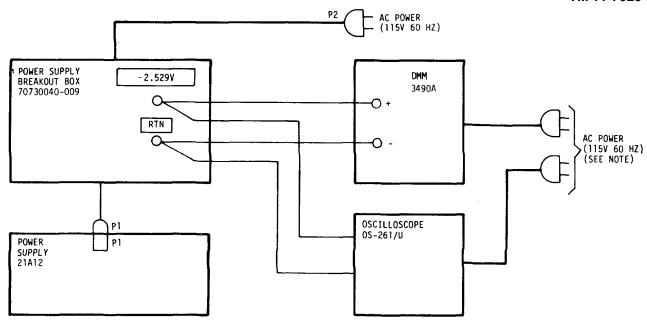

| 4-4              | DC power supply circuits troubleshooting setup diagram                                | 4-18        |

| 4-5              | Power supply waveforms diagram                                                        | 4-19        |

| 4-6              | Cable power supply circuits troubleshooting setup diagram                             | 4-20        |

| 4-7              | Typical heat sink transistor, diode, and SCR installation and removal diagram         | 4-21        |

| 4-8              | Handle mounting diagram                                                               | 4-25        |

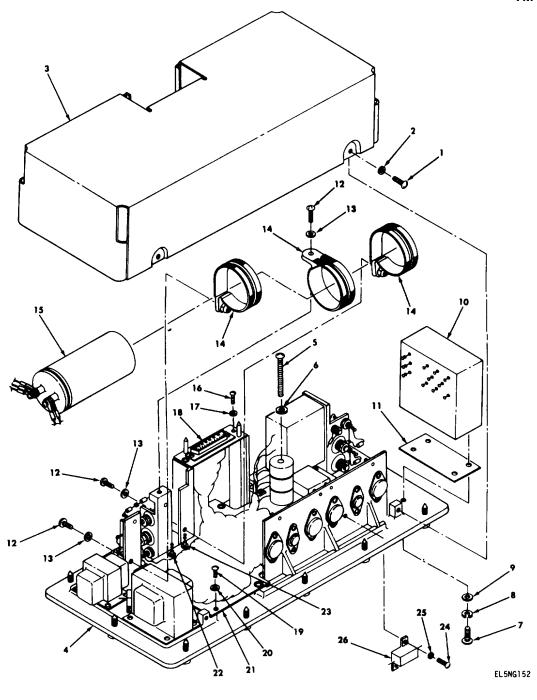

| 4-9              | Power supply disassembly diagram                                                      | 4-27        |

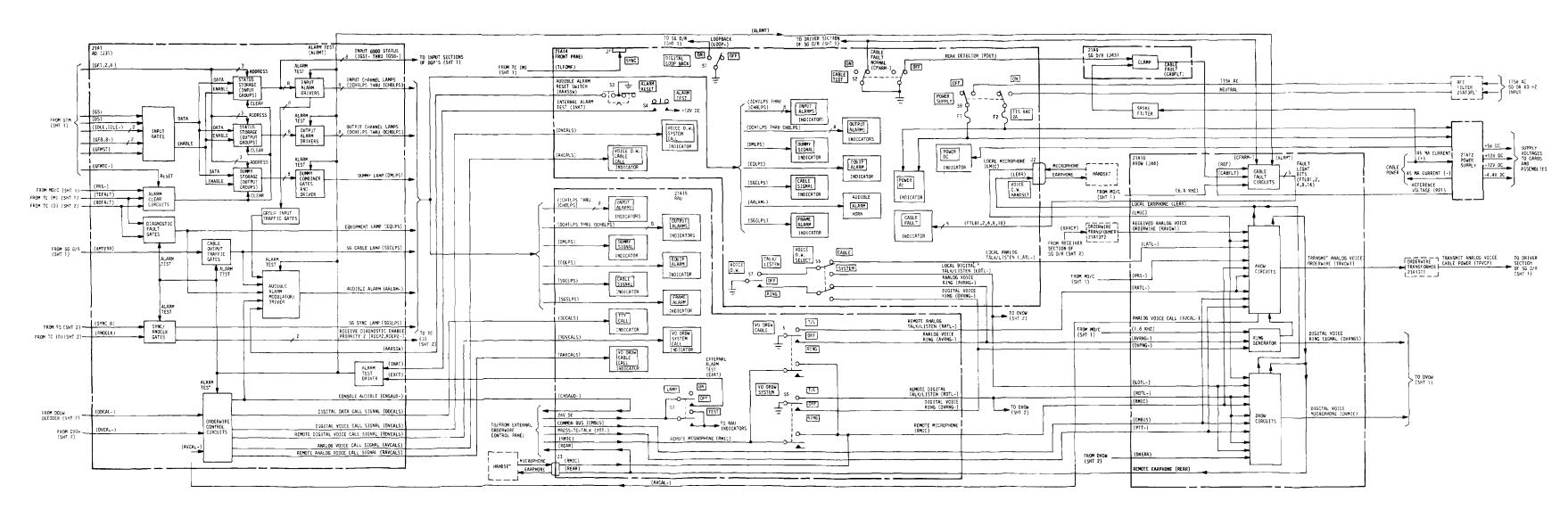

| FO-1             | TD-976/G overall block diagram (3 sheets)                                             | *           |

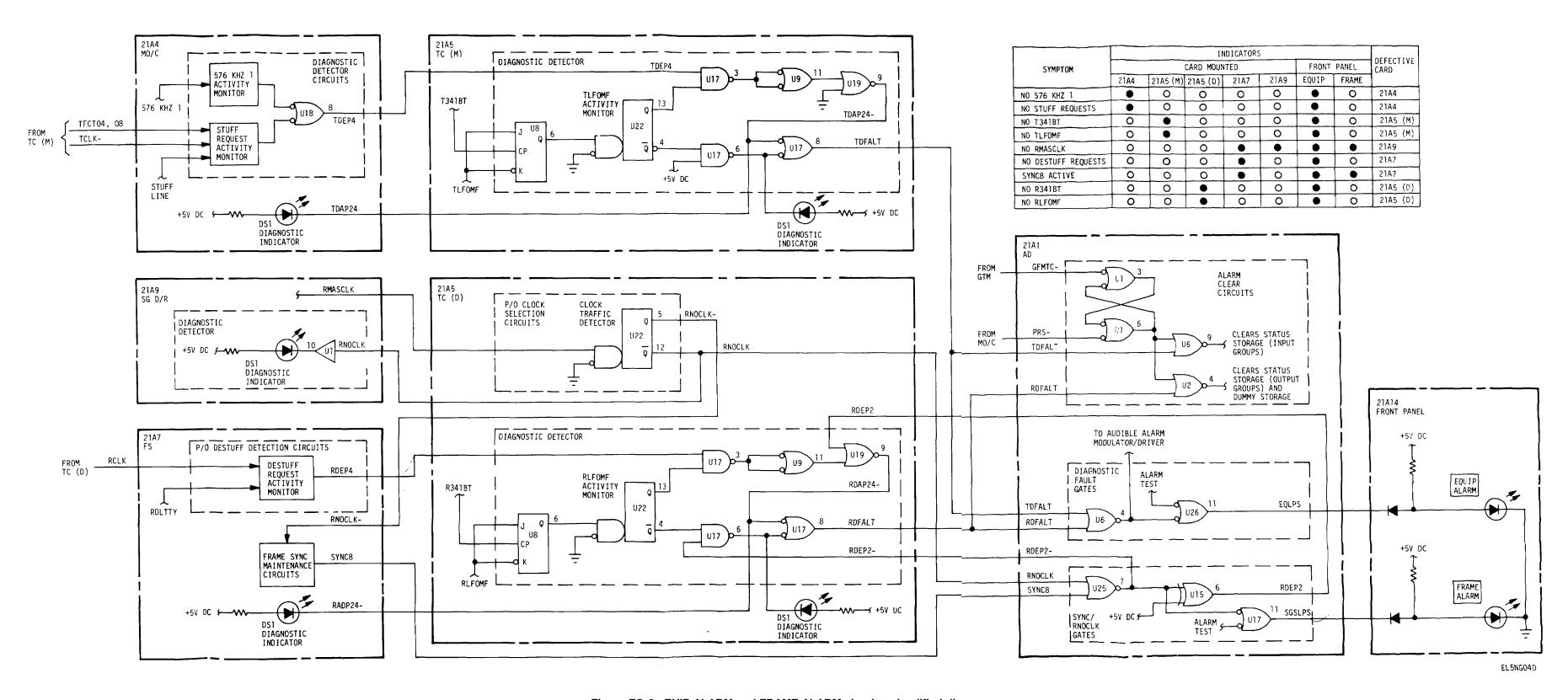

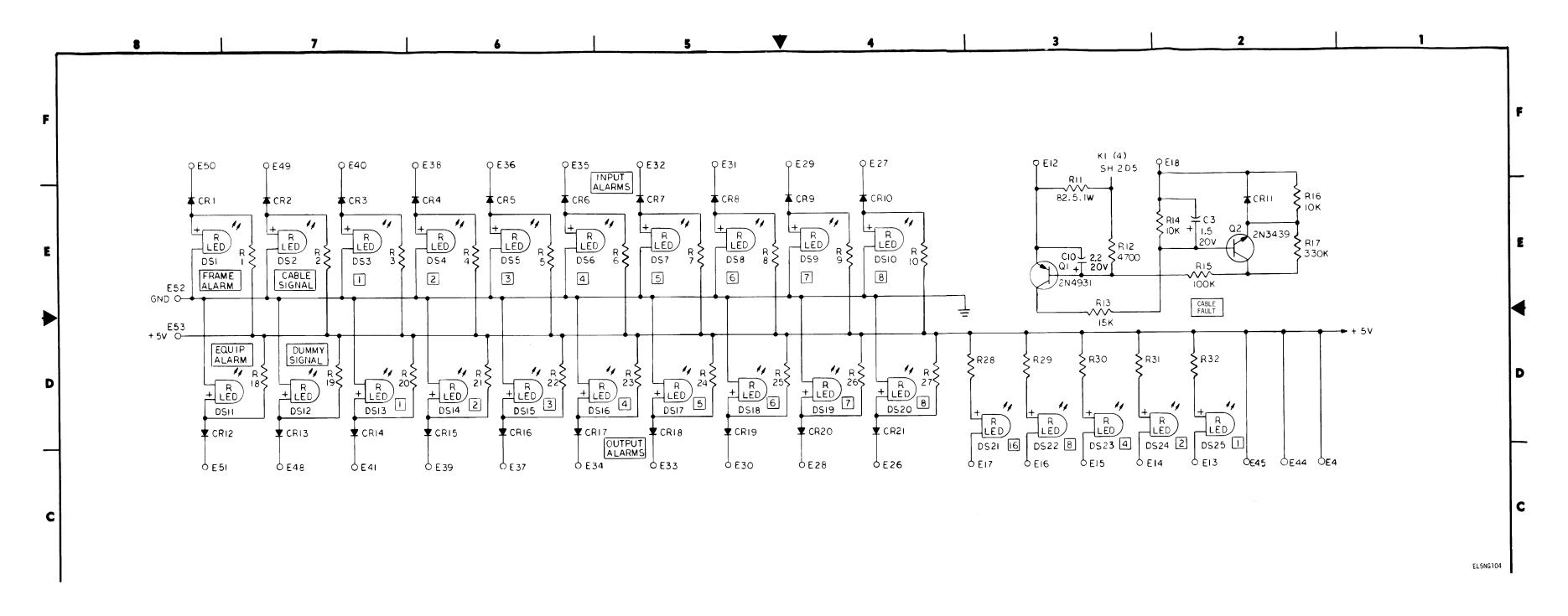

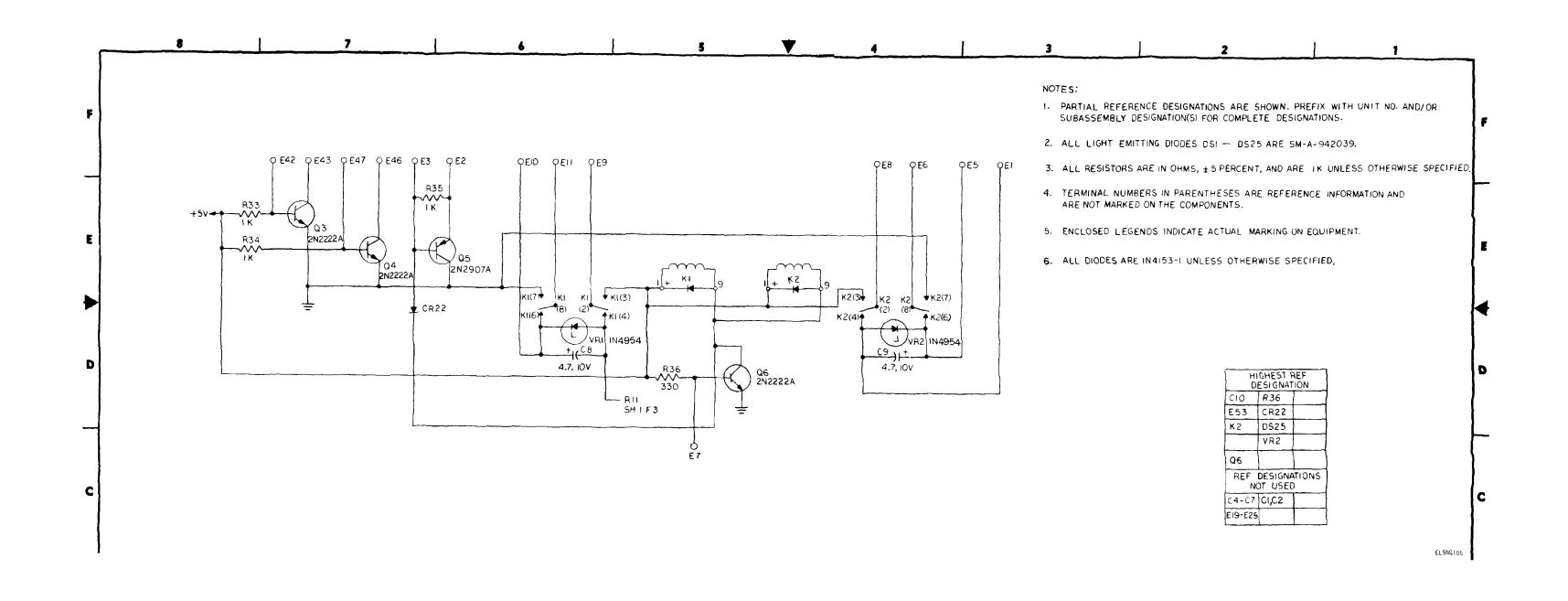

| FO-2             | EQUIP ALARM and FRAME ALARM circuits, simplified diagram                              | *           |

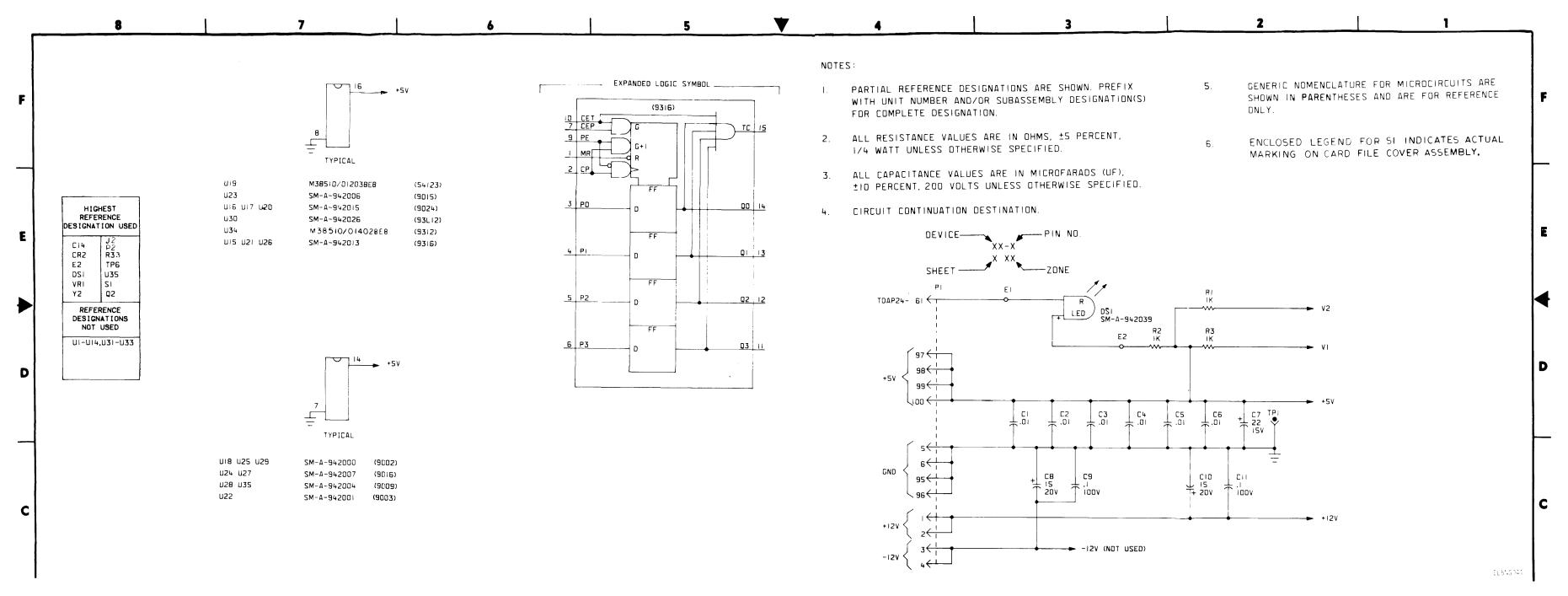

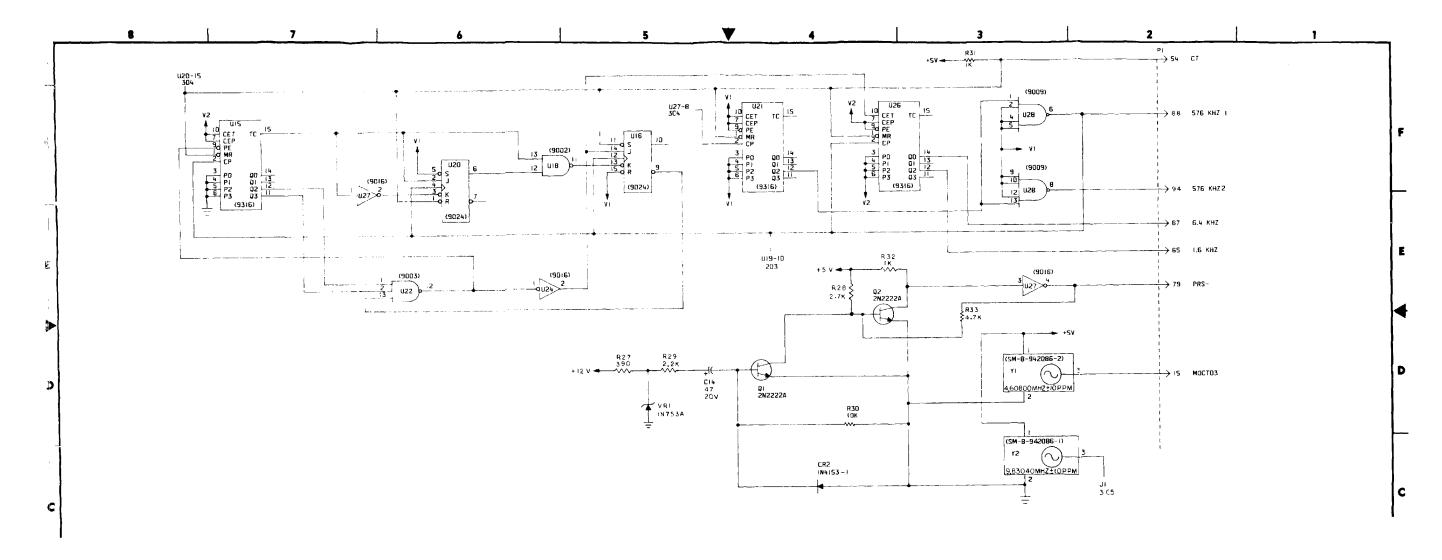

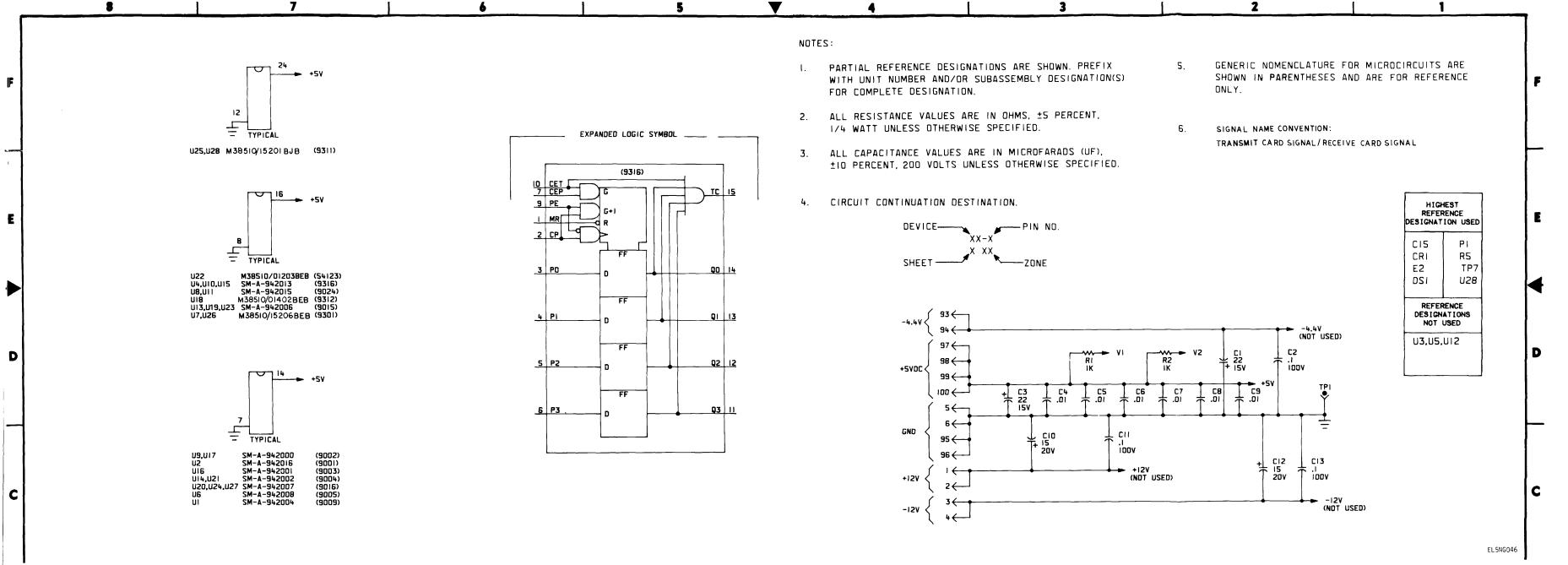

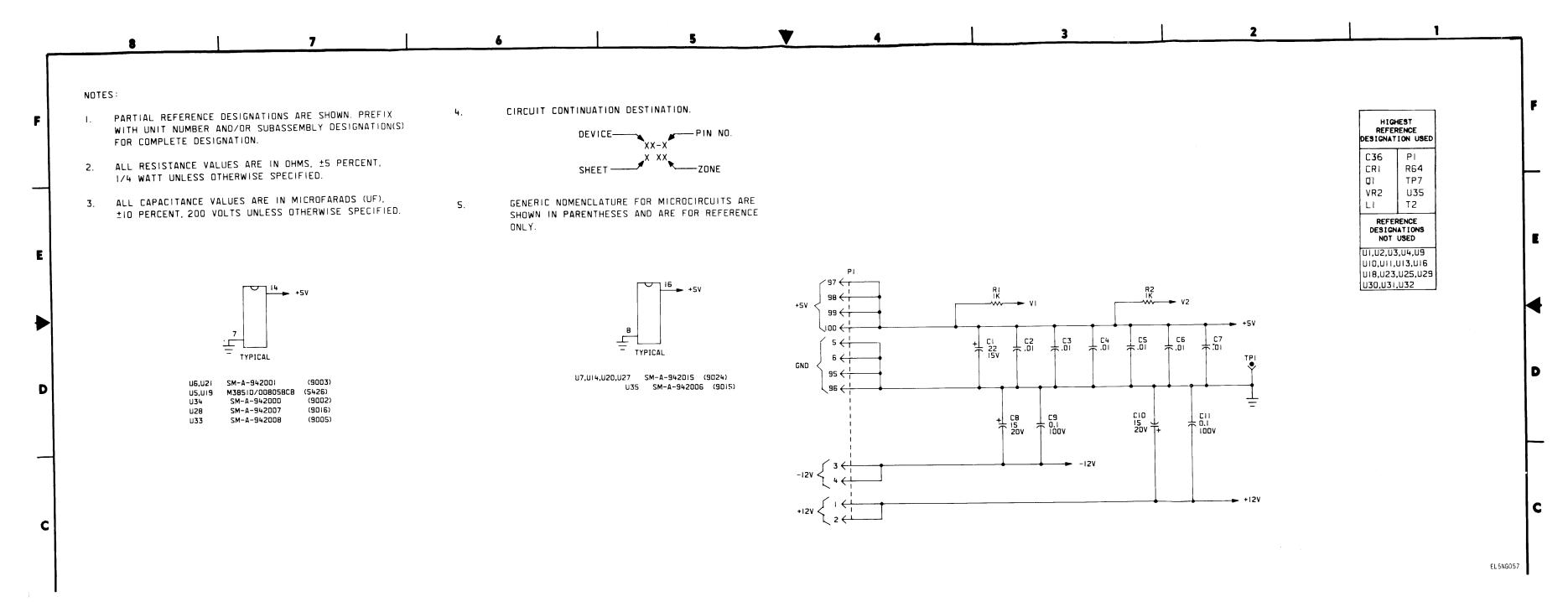

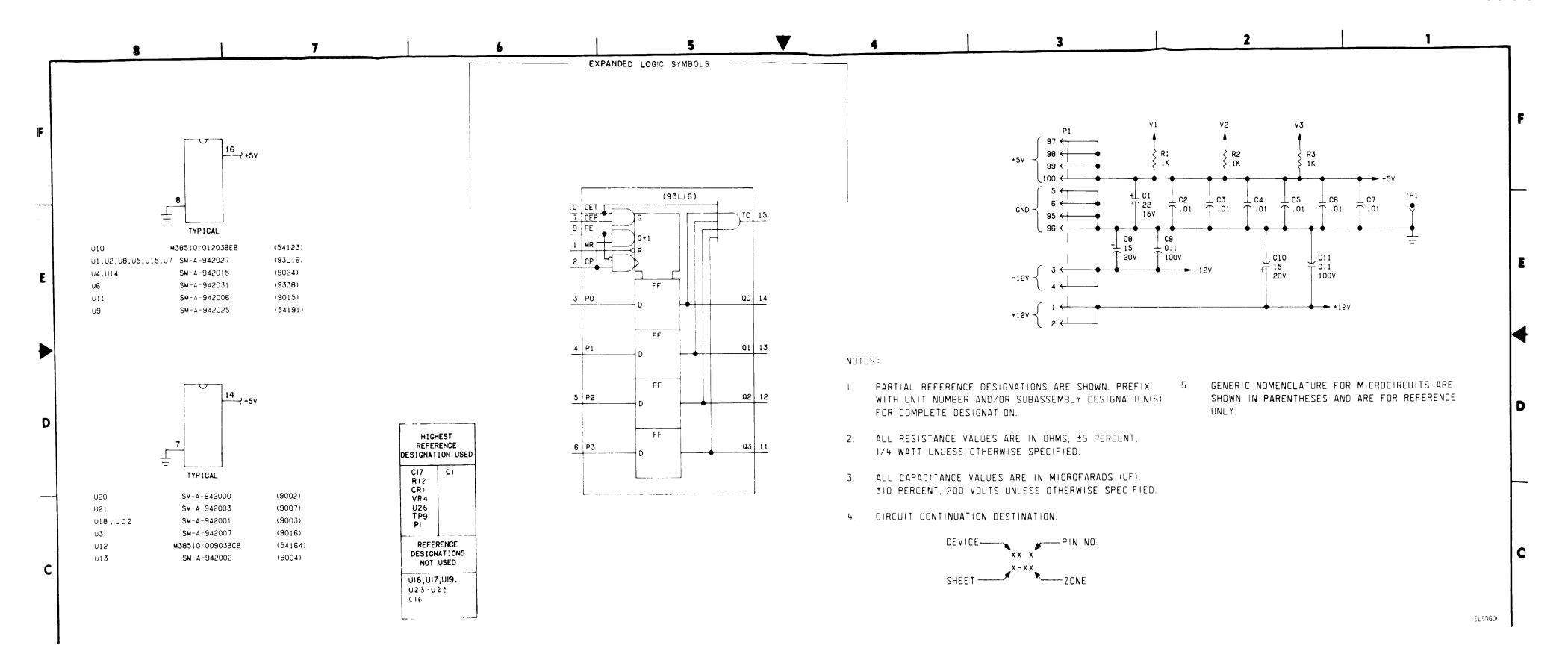

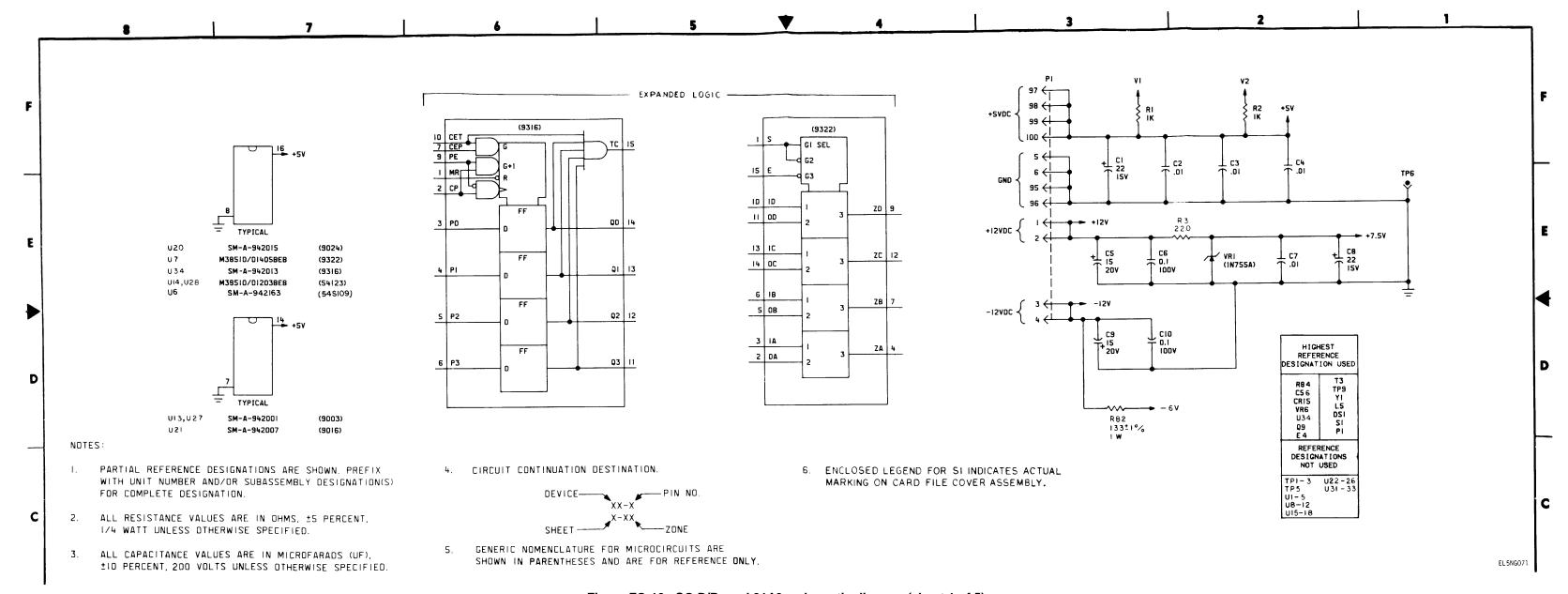

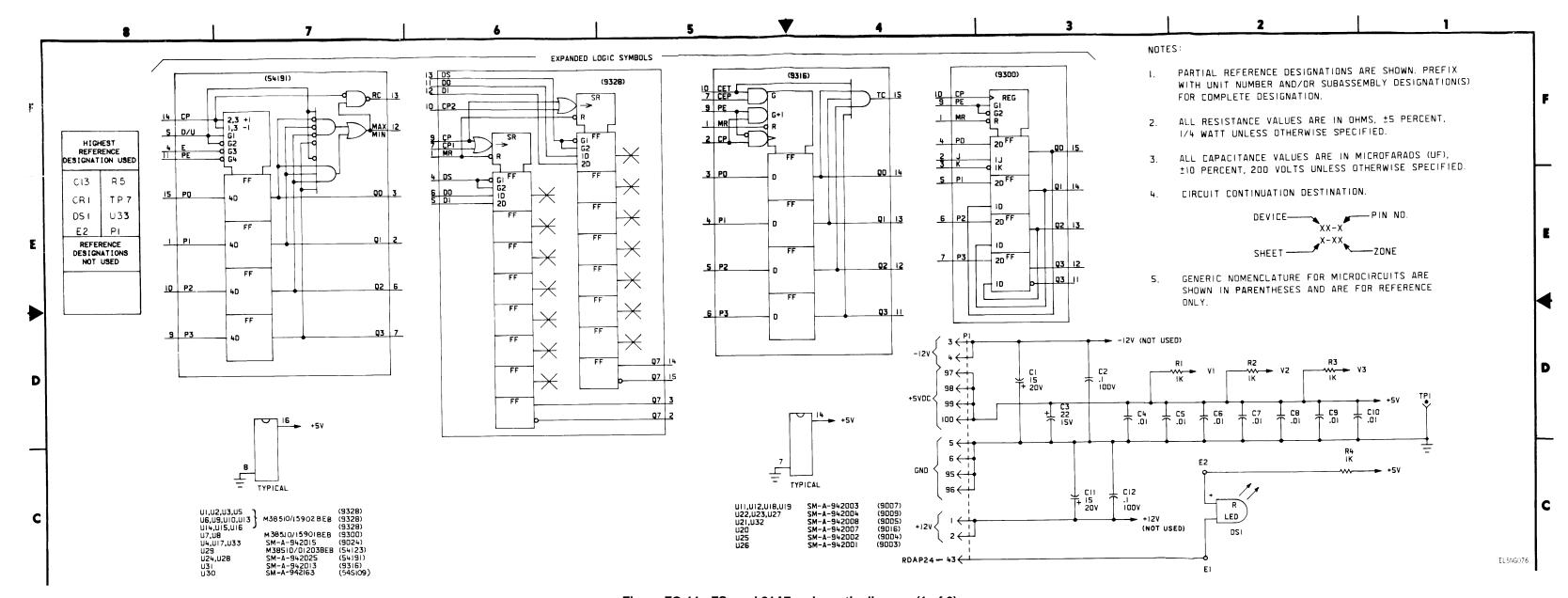

| FO-3             | MOIC card 21A4, schematic diagram (4 sheets)                                          | *           |

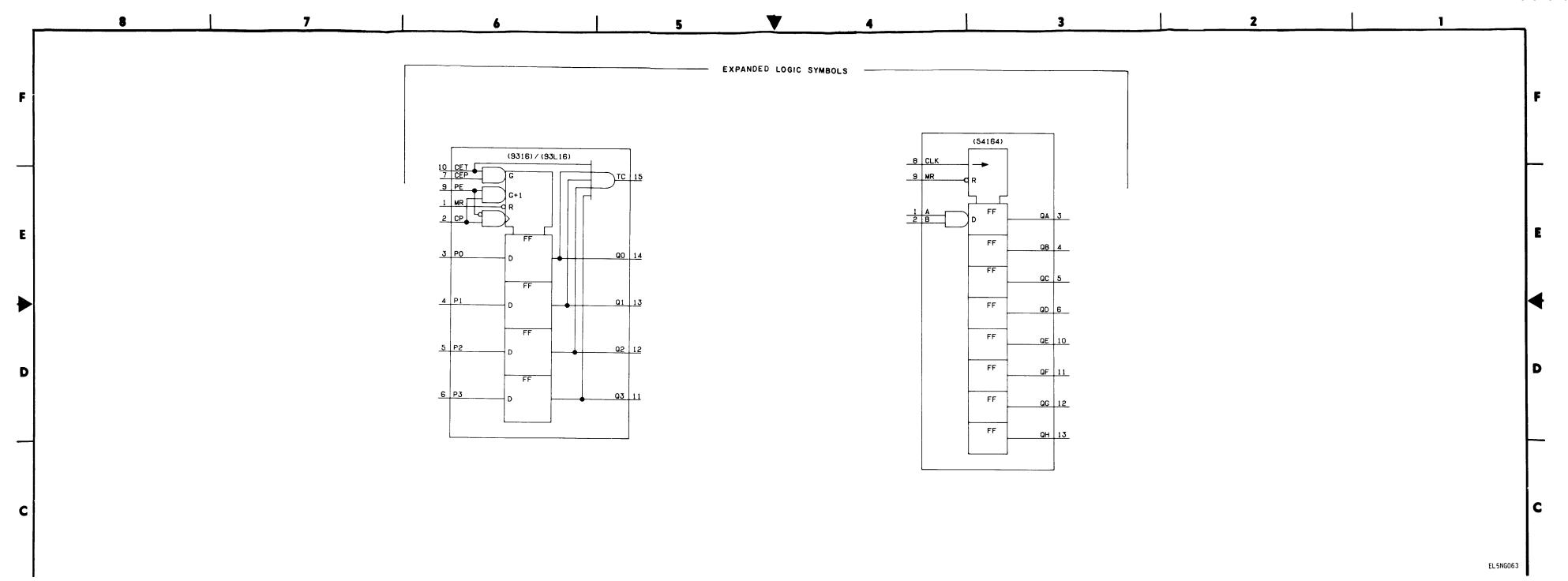

| FO-4             | TC card 21A5, block diagram                                                           | *           |

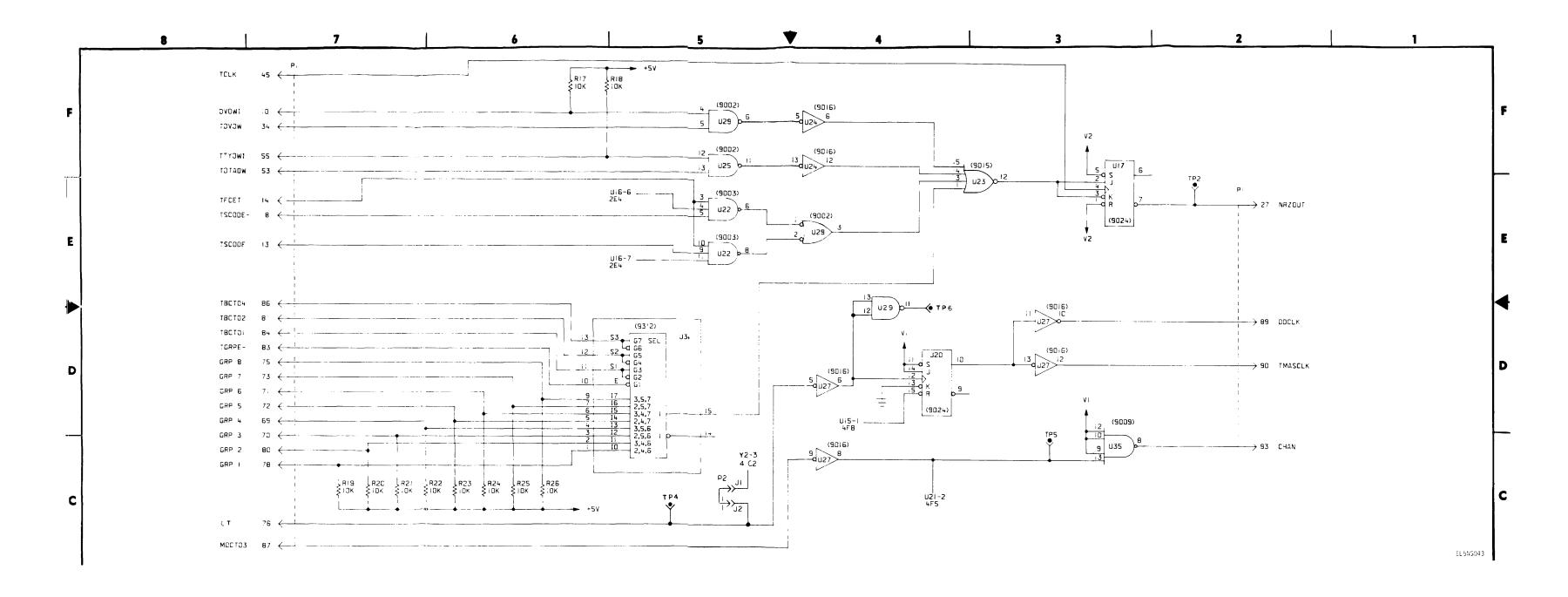

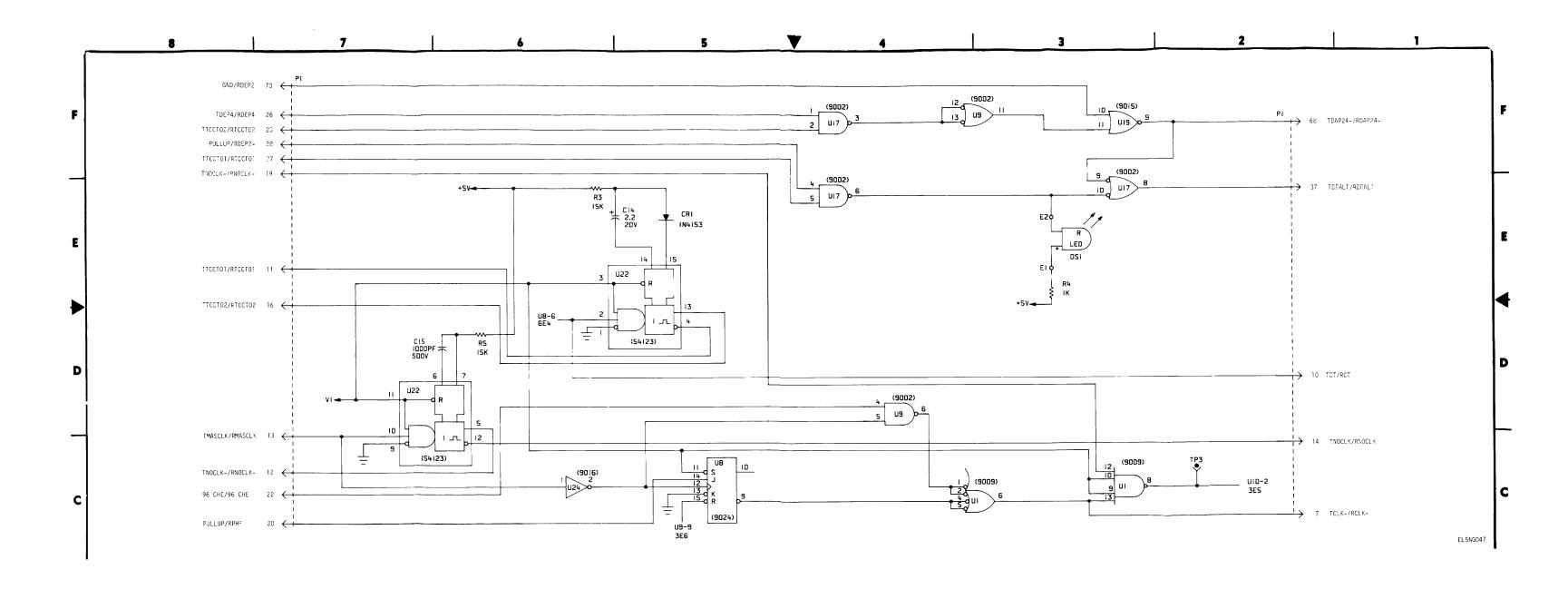

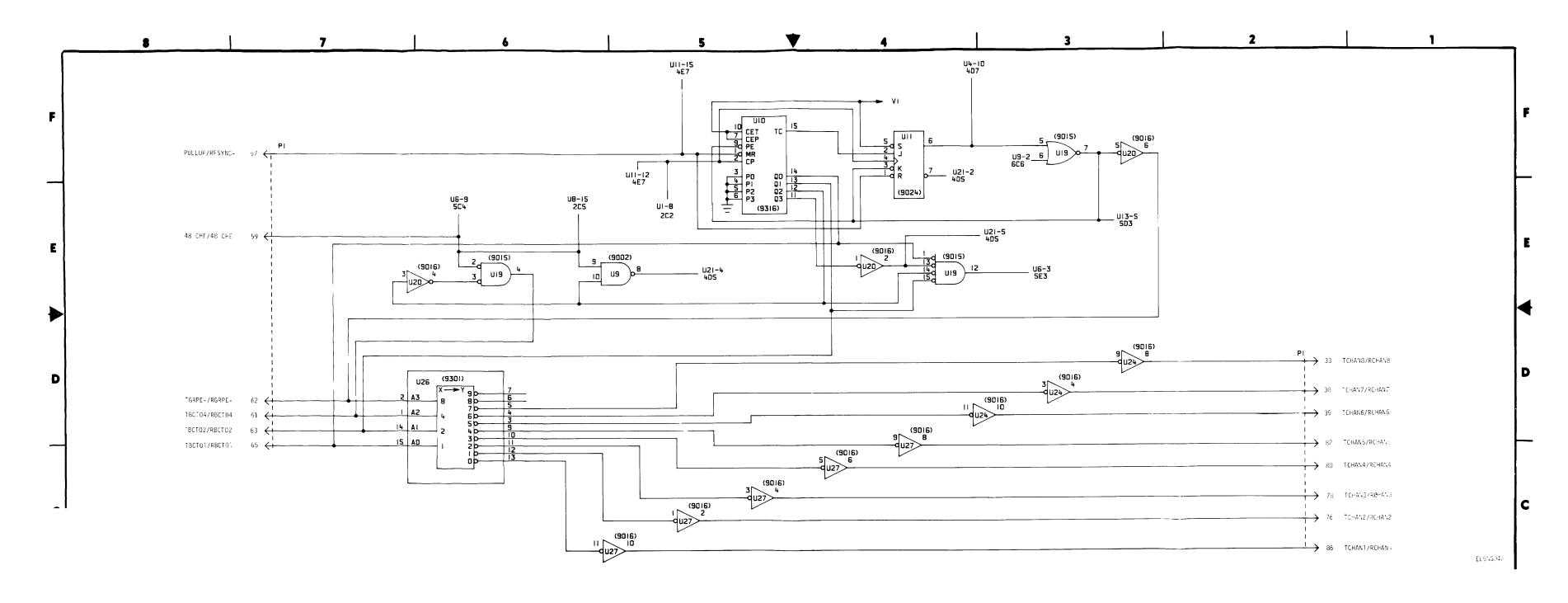

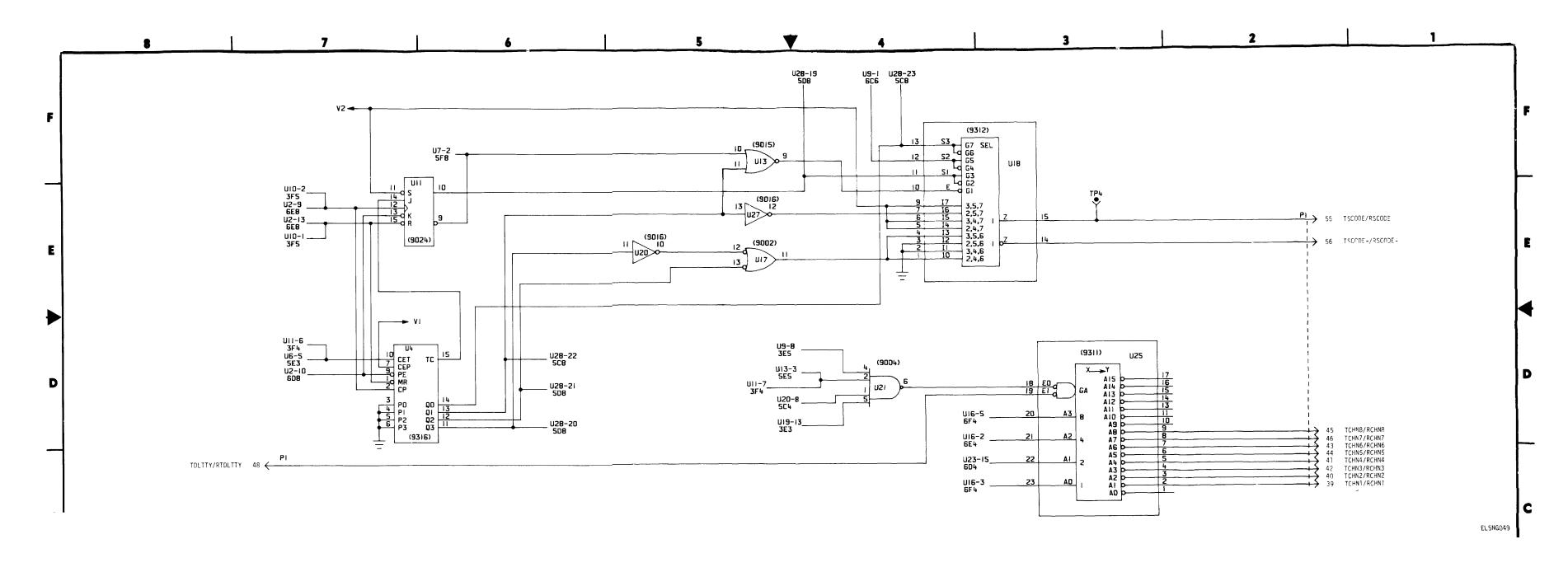

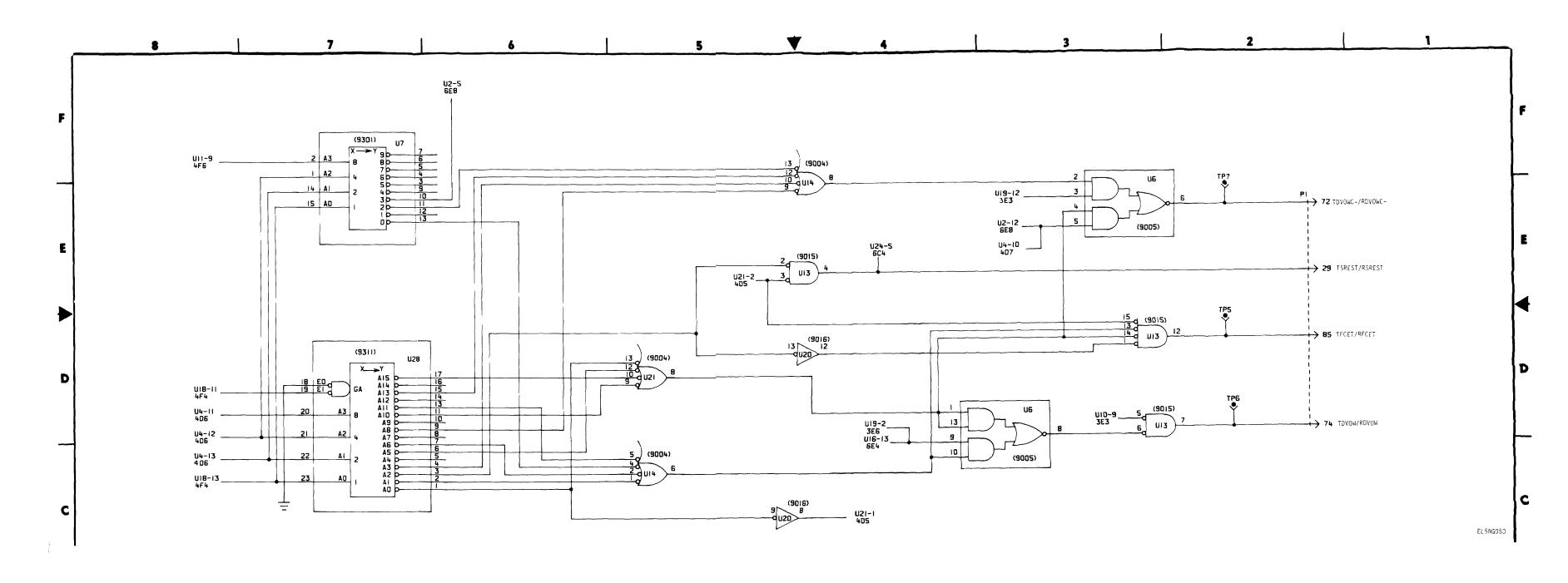

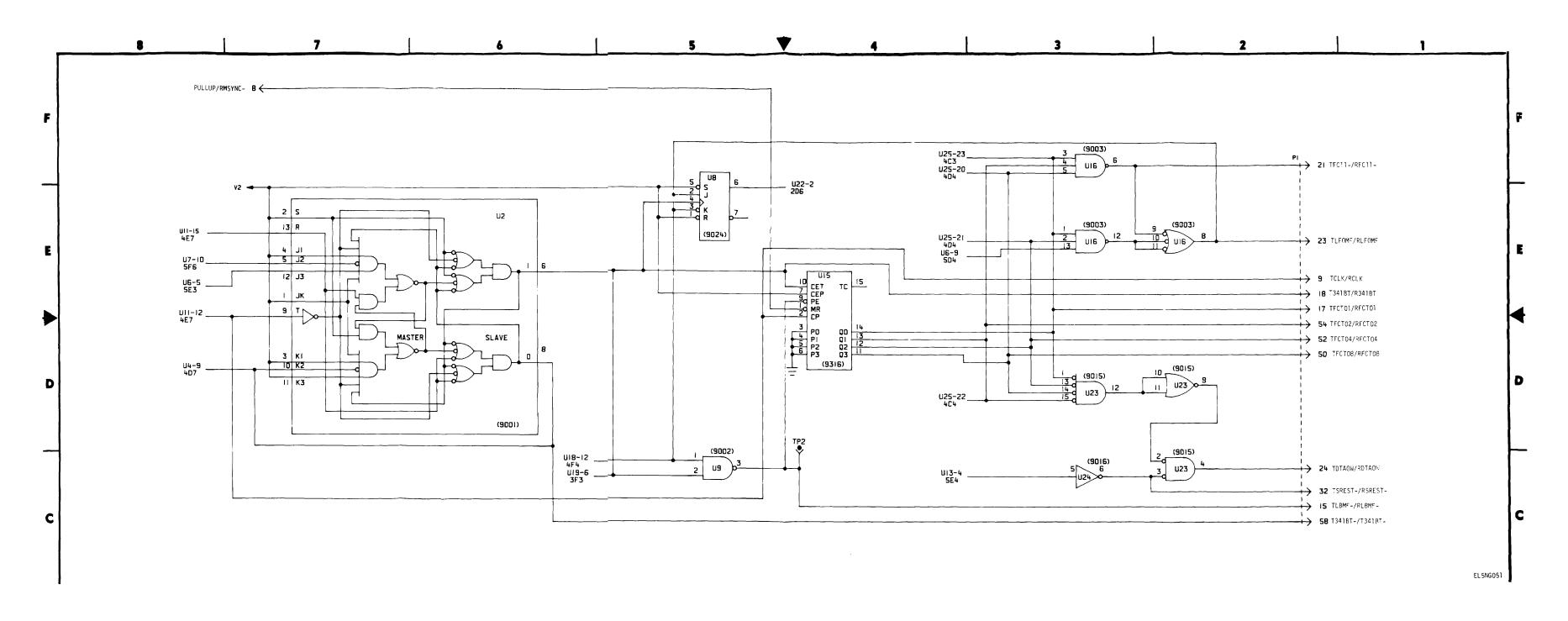

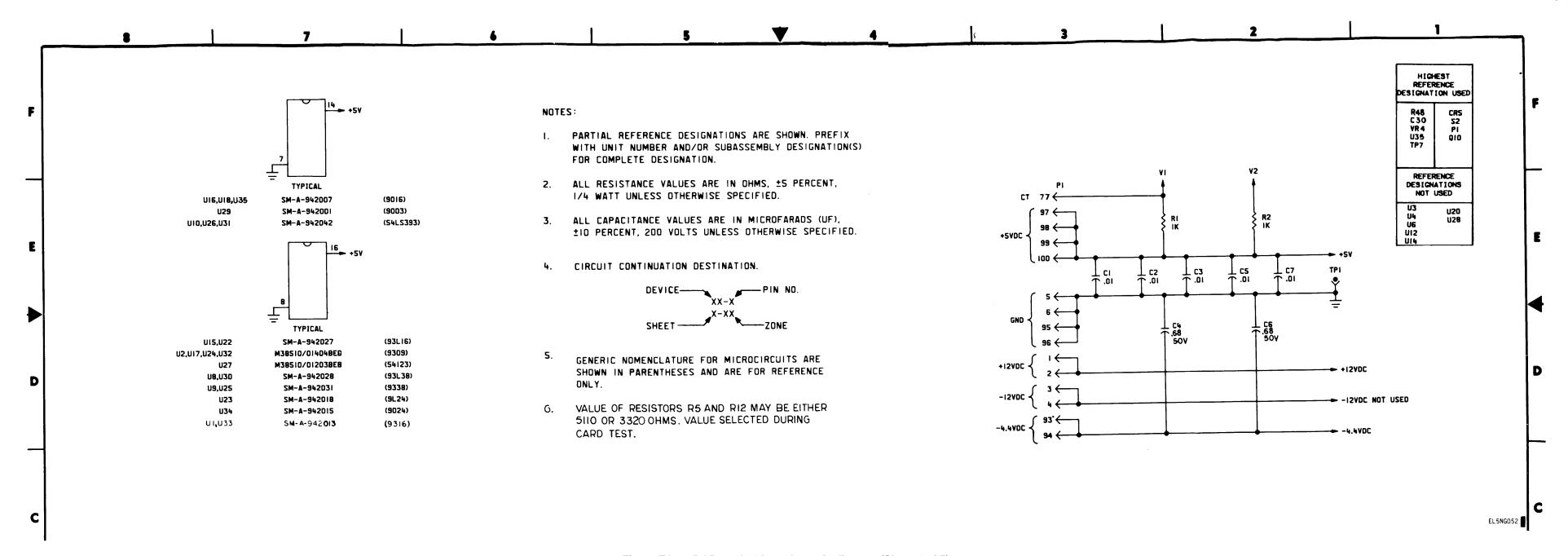

| FO-5             | TC card 21A5, schematic diagram (6 sheets)                                            | *           |

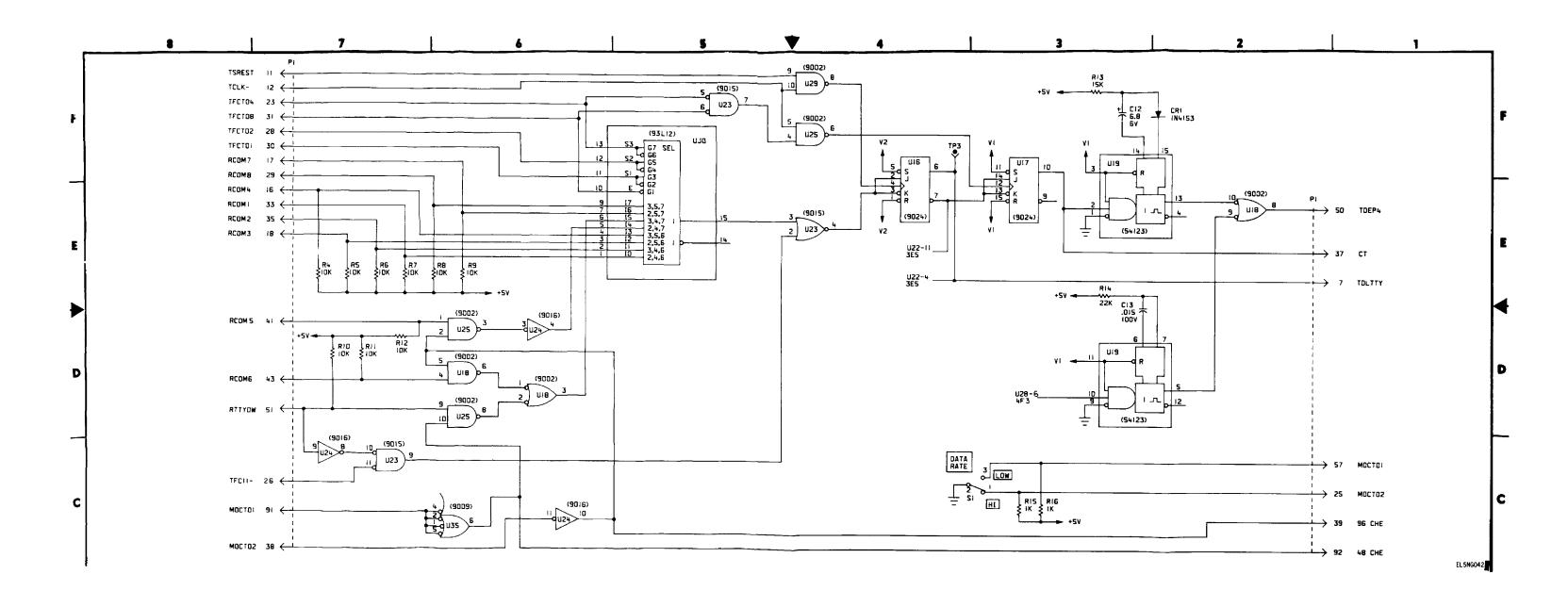

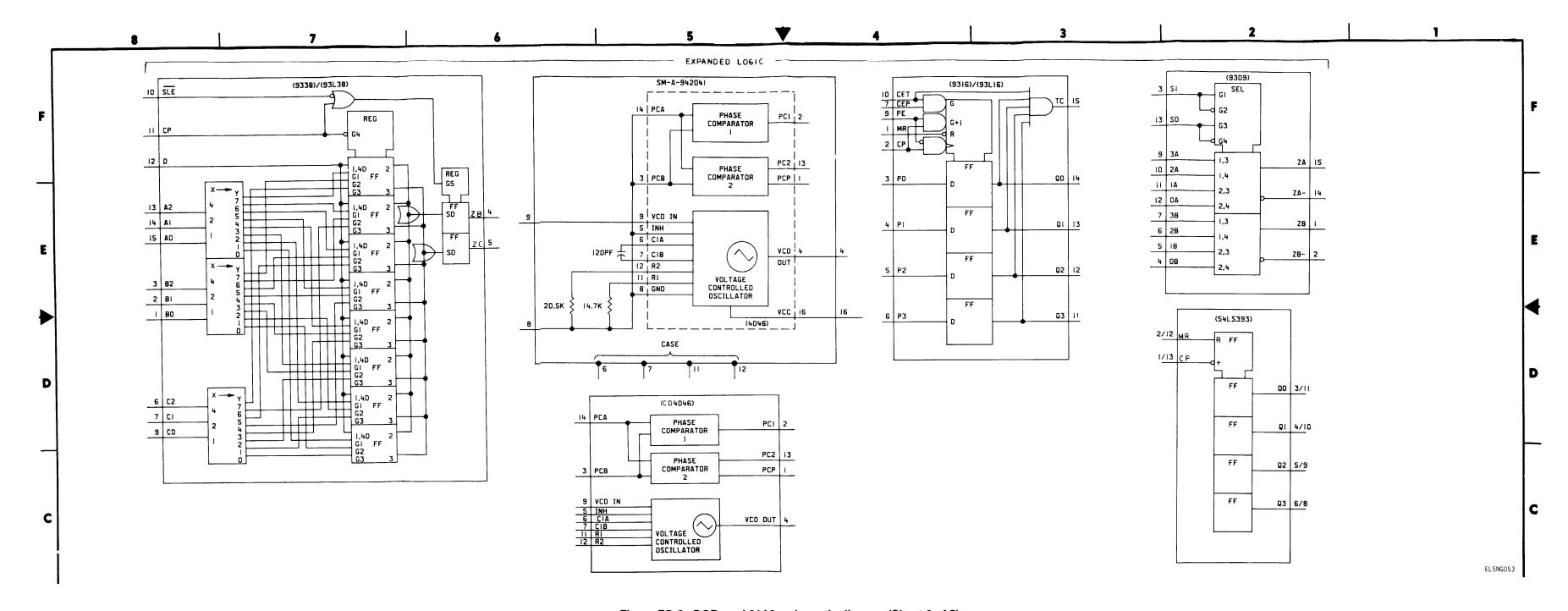

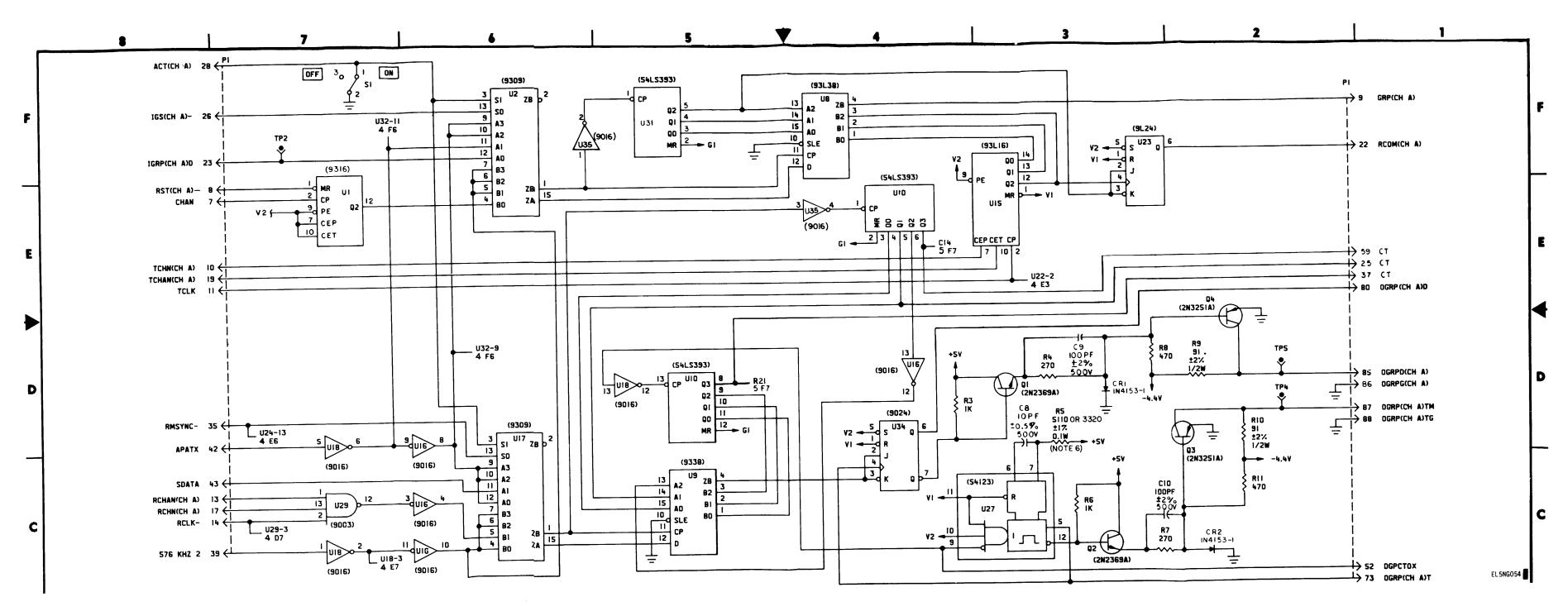

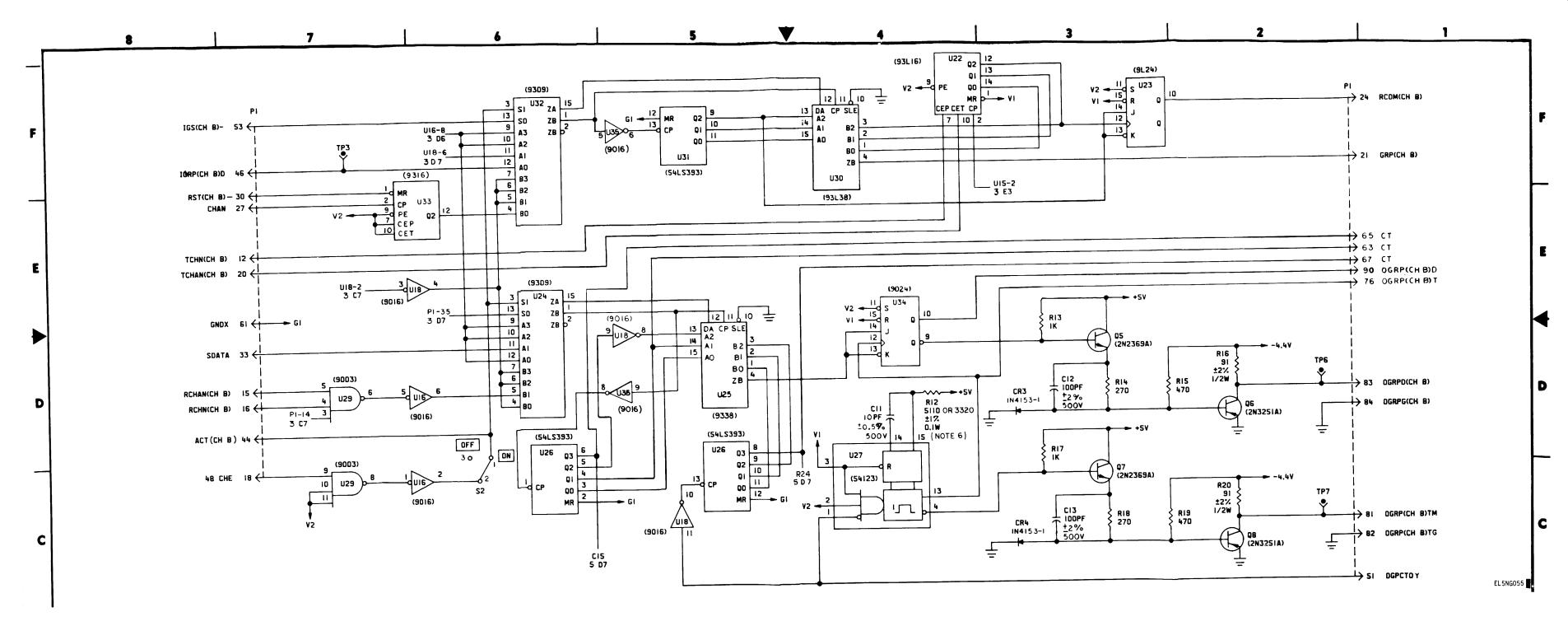

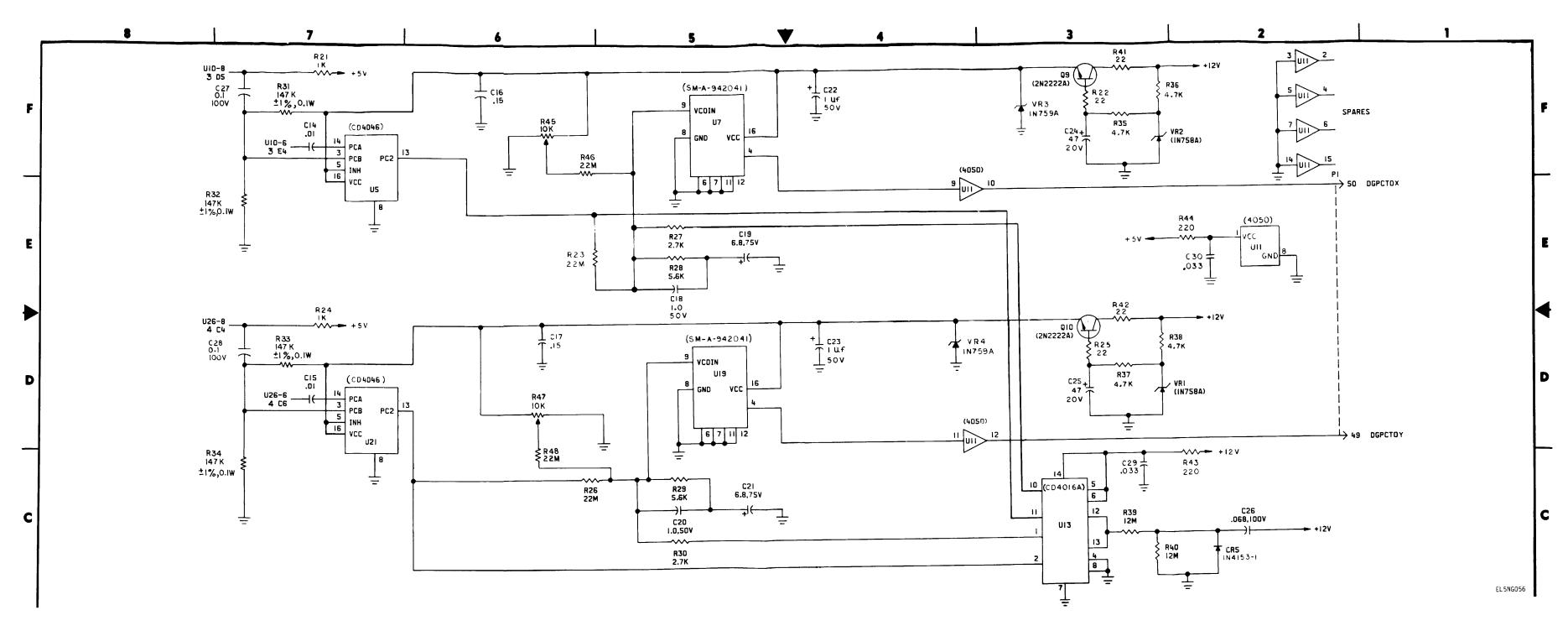

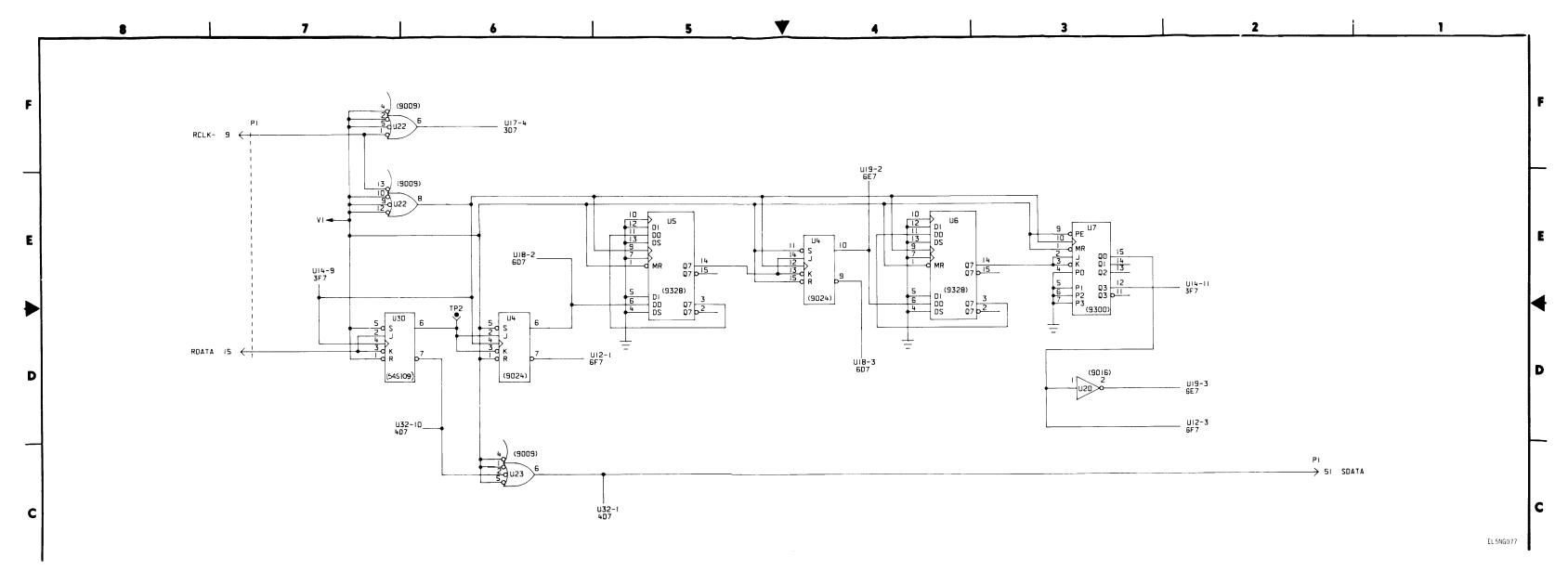

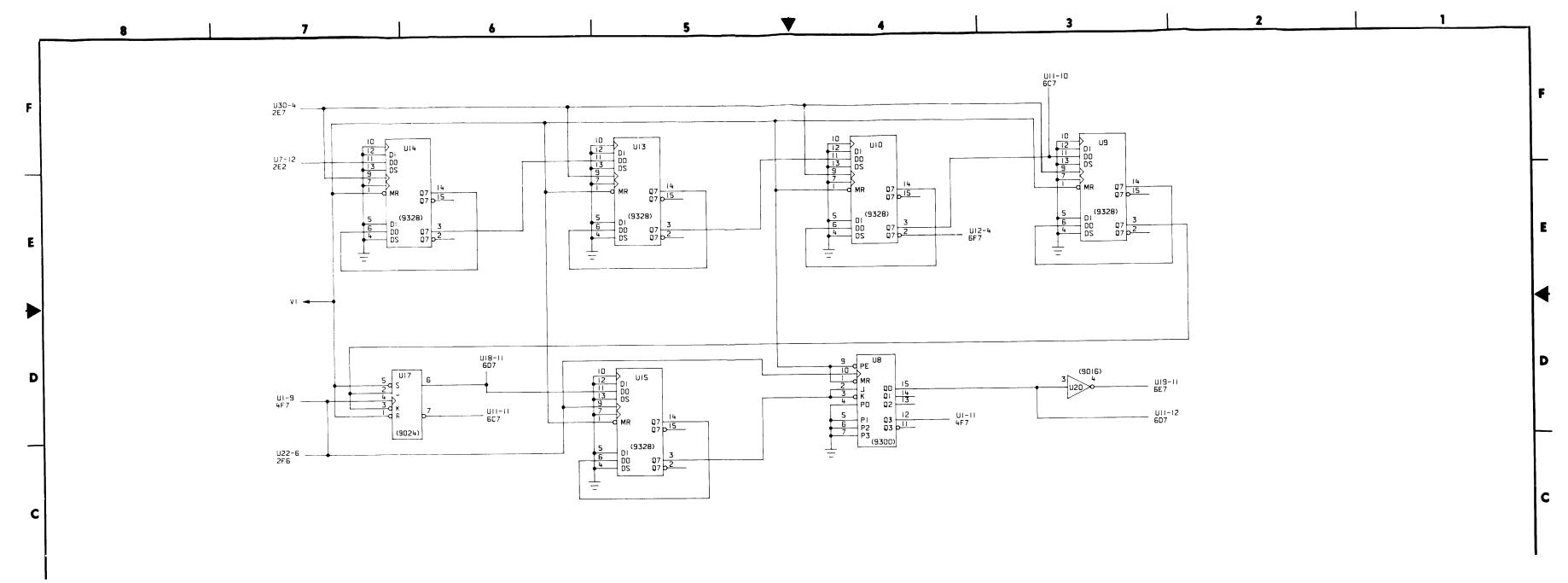

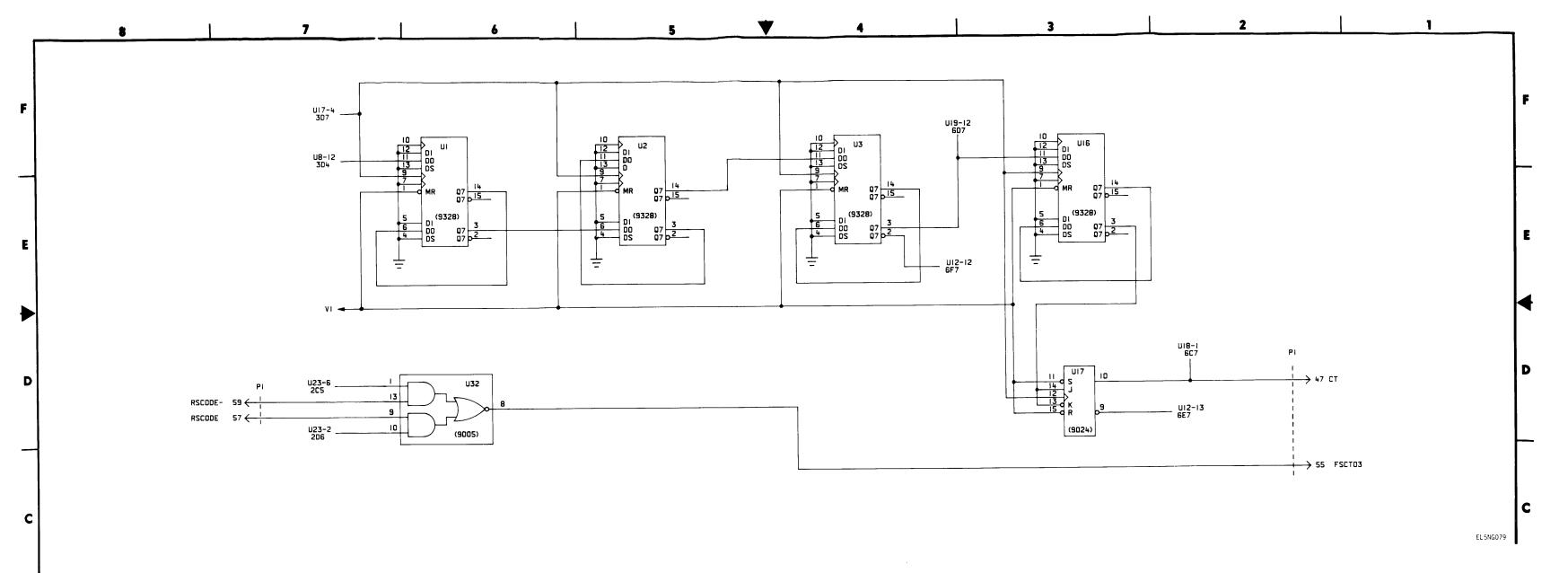

| FO-6             | DGP card 21A6, schematic diagram (5 sheets)                                           | *           |

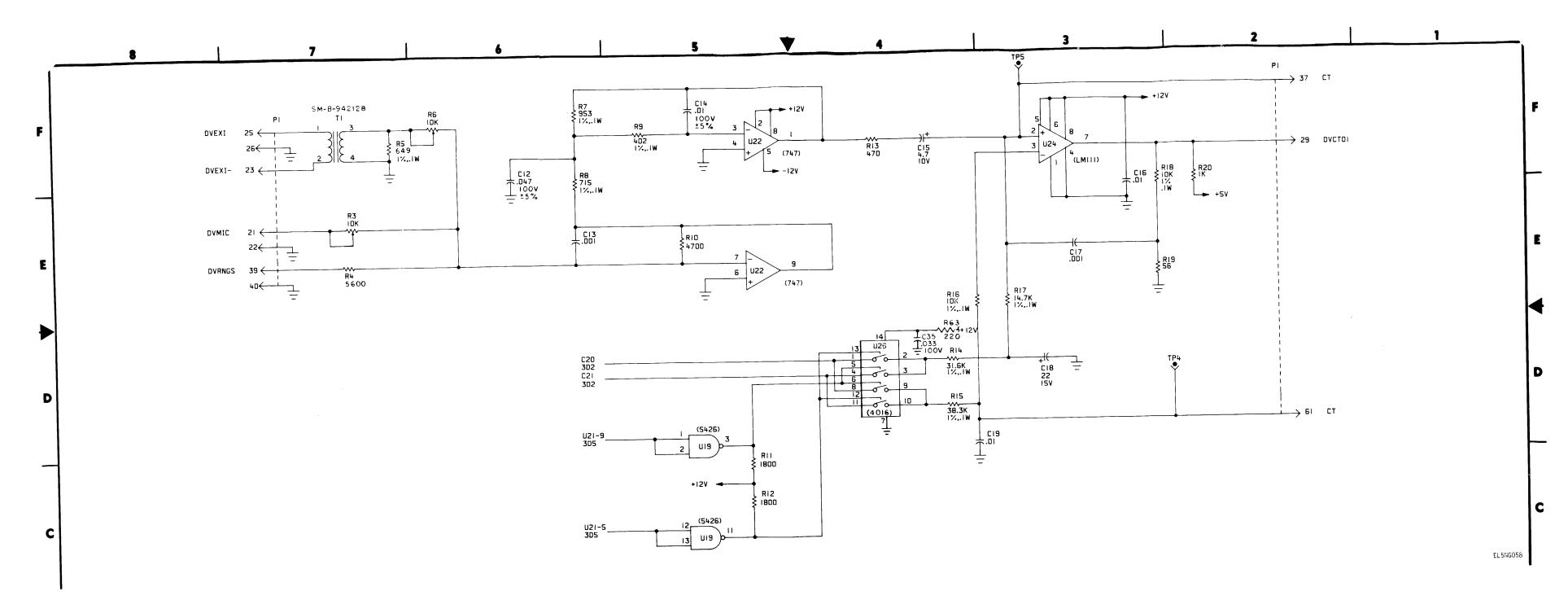

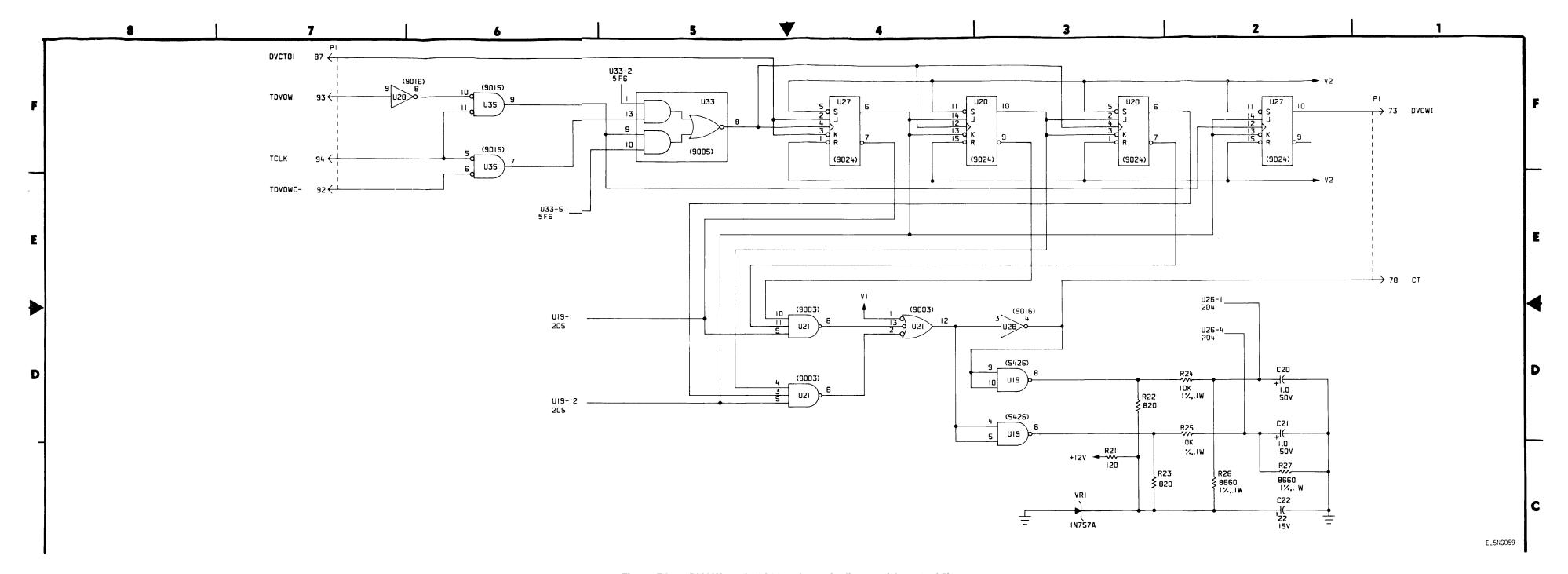

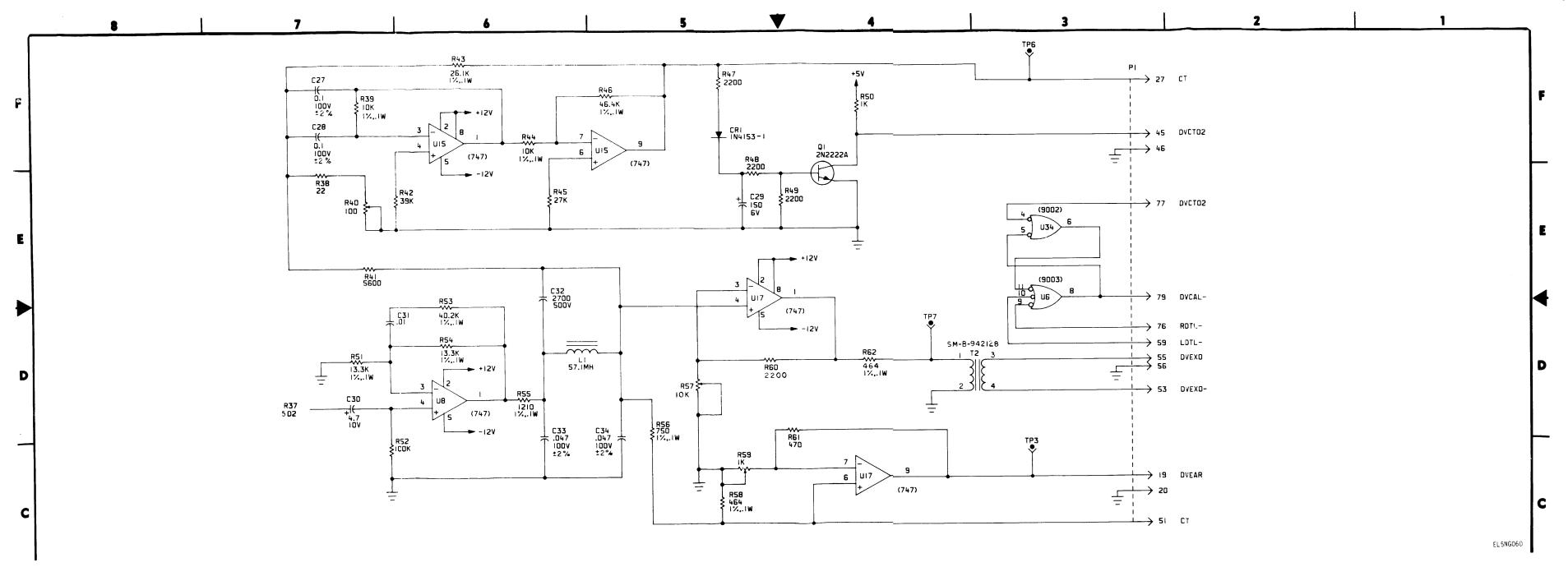

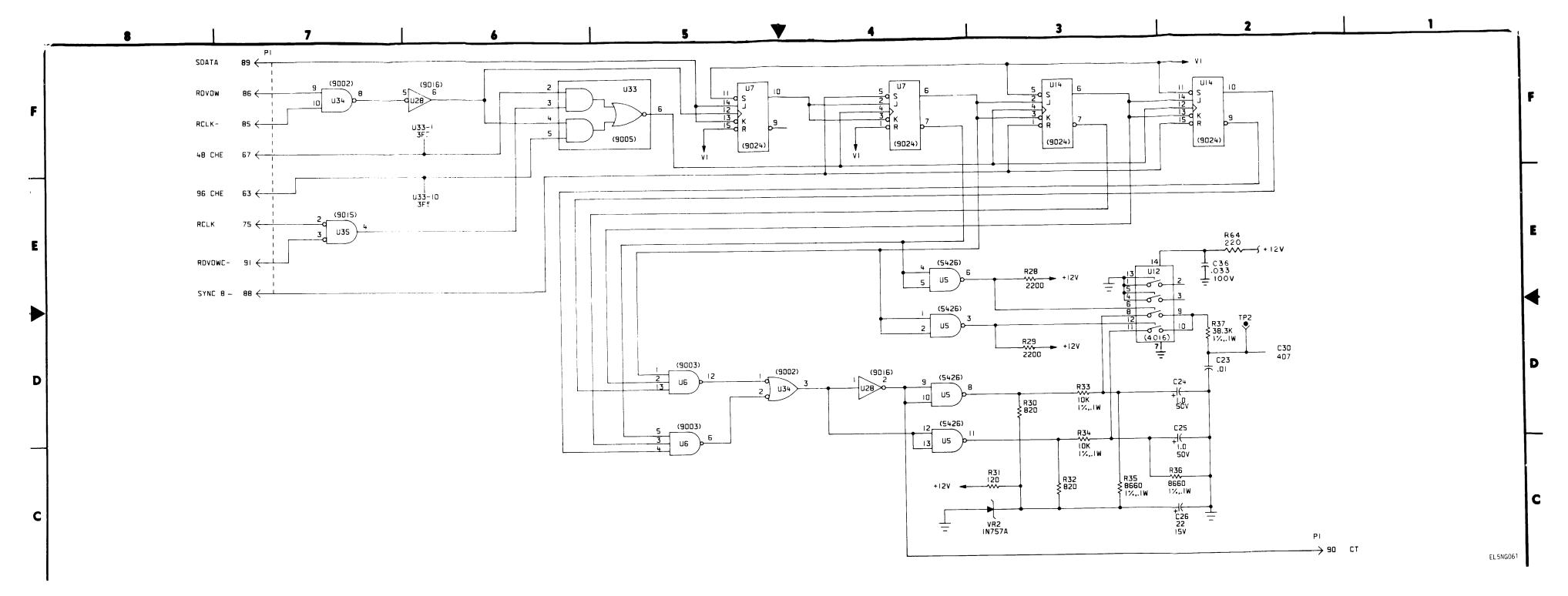

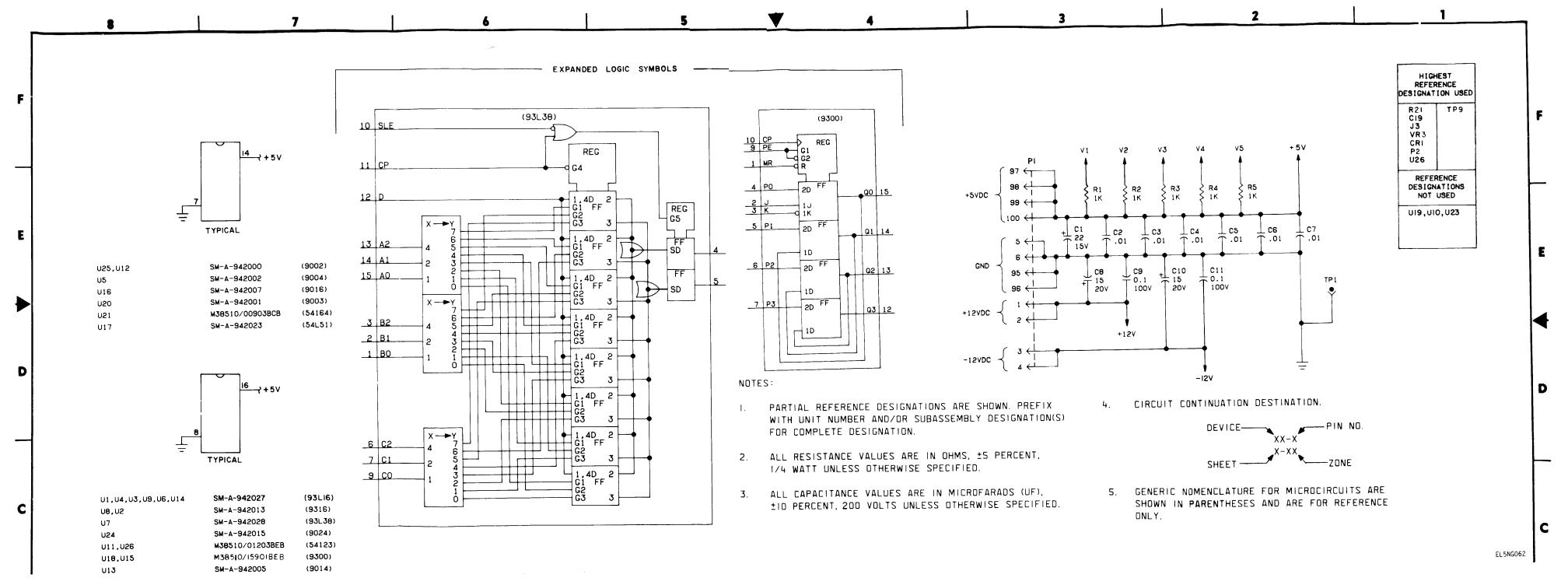

| FO-7             | DVOW card 21All, schematic diagram (5 sheets)                                         | *           |

| FO-8             | DDOW encoder card 21A3, schematic diagram (5 sheets)                                  | *           |

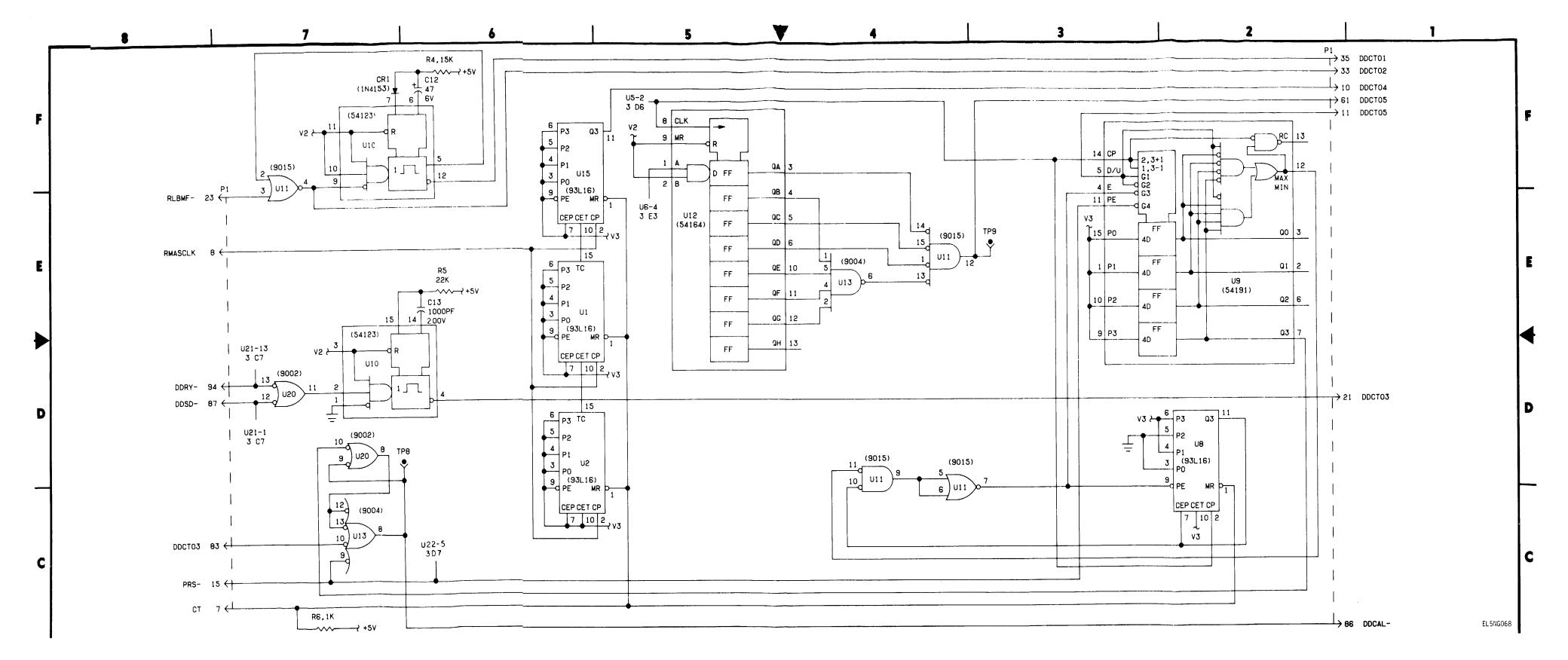

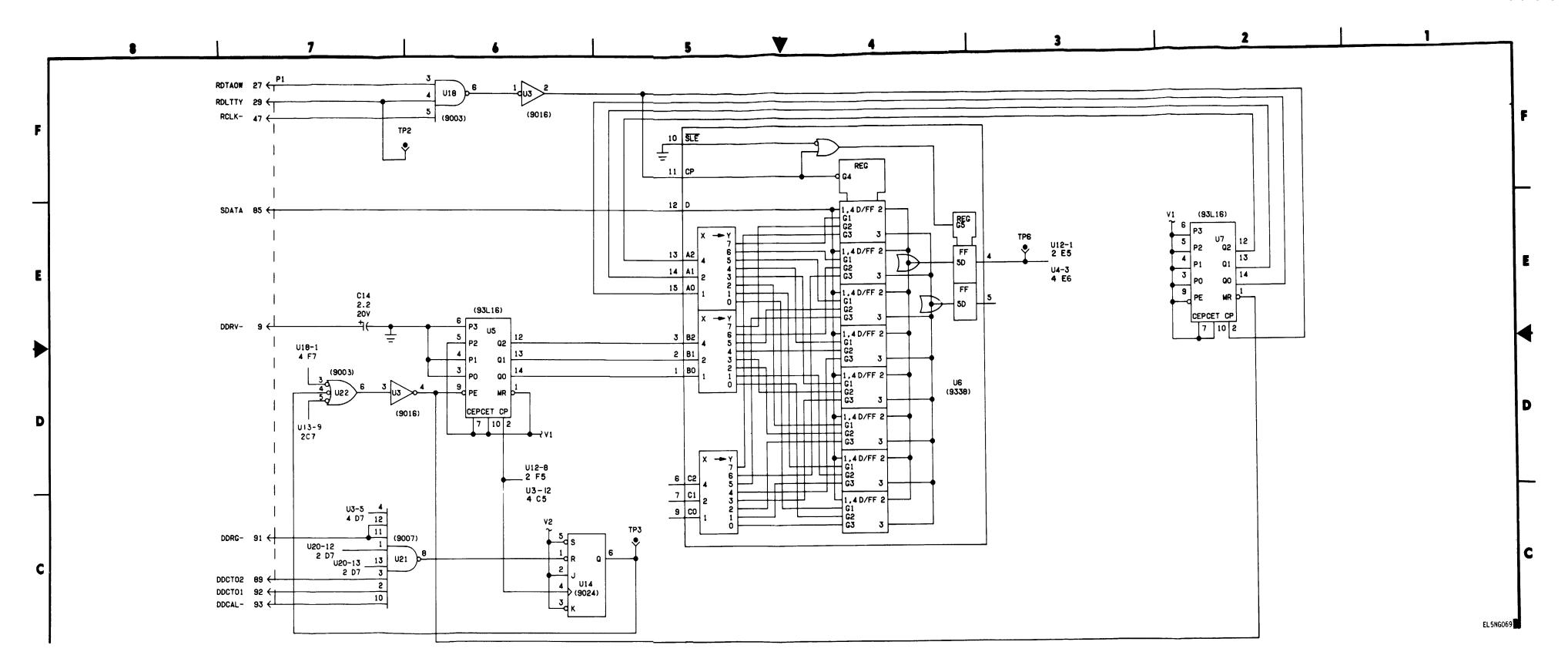

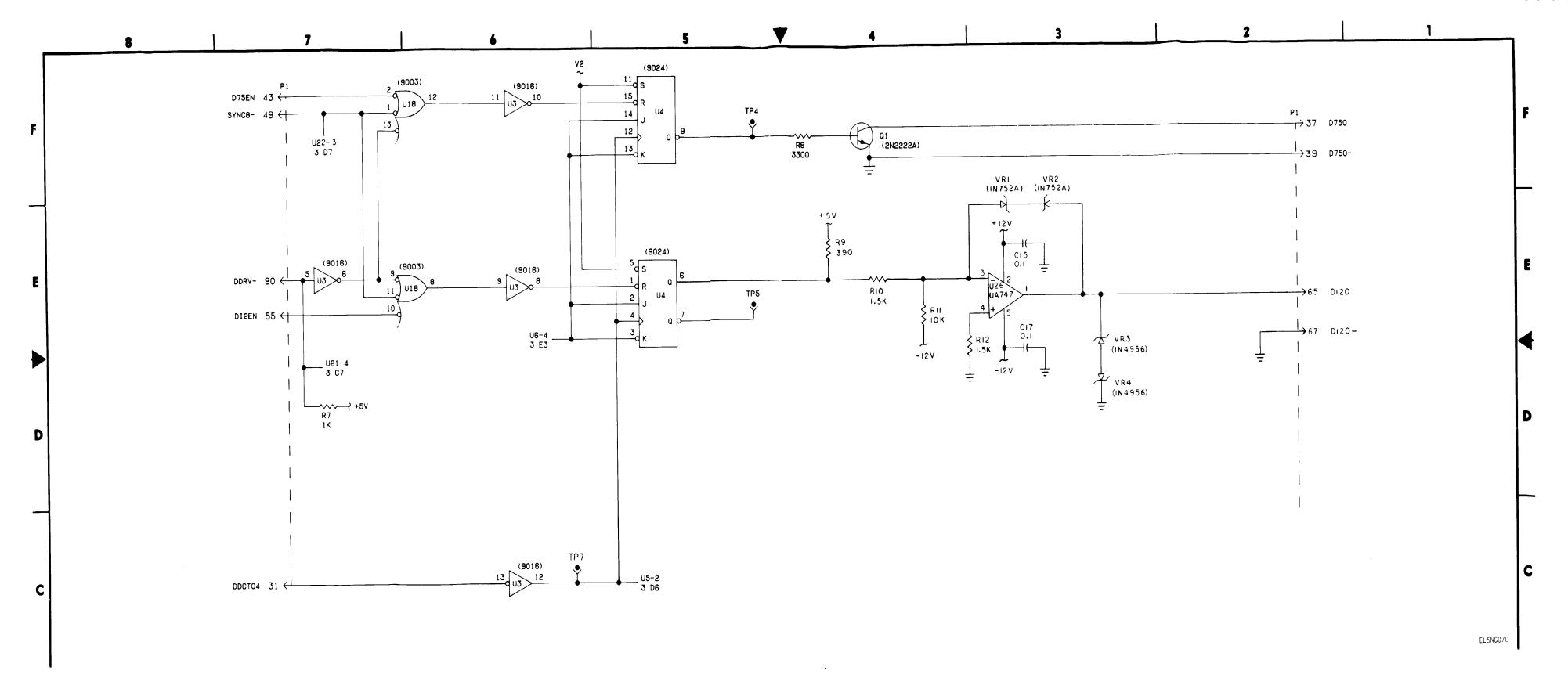

| FO-9             | DDOW decoder card 21A8, schematic diagram (4 sheets)                                  | *           |

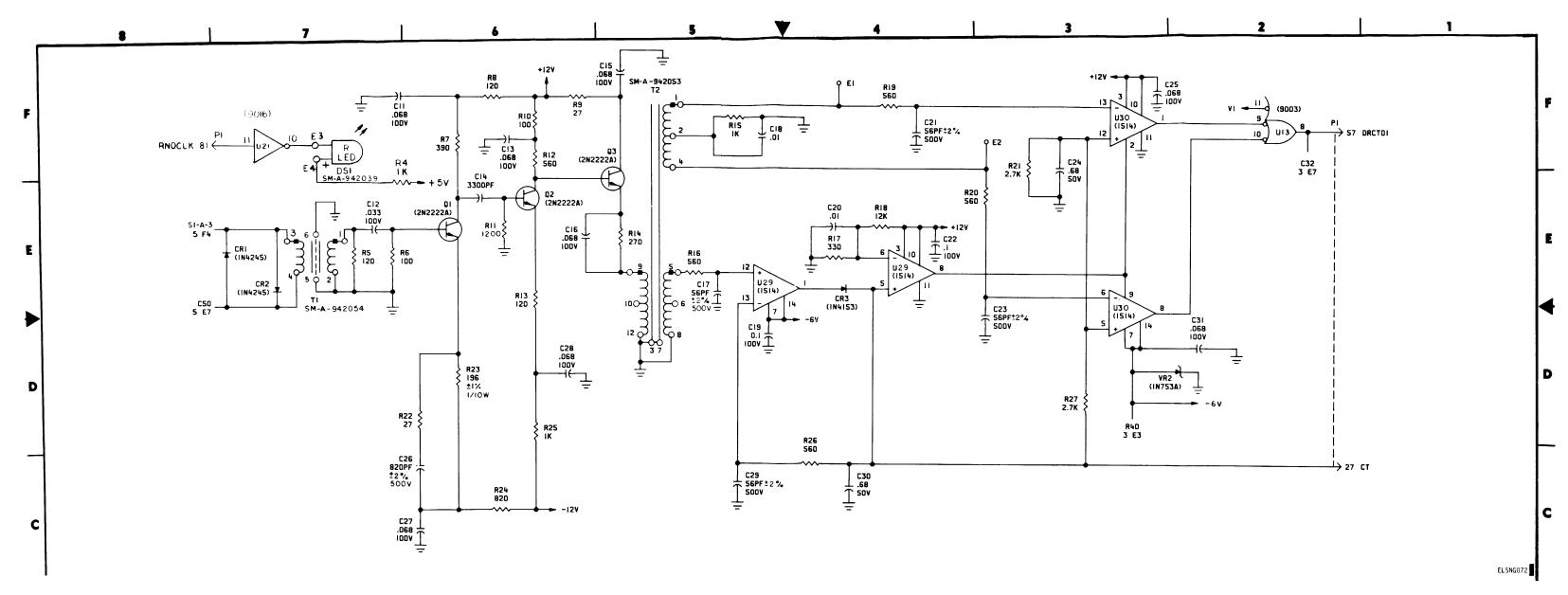

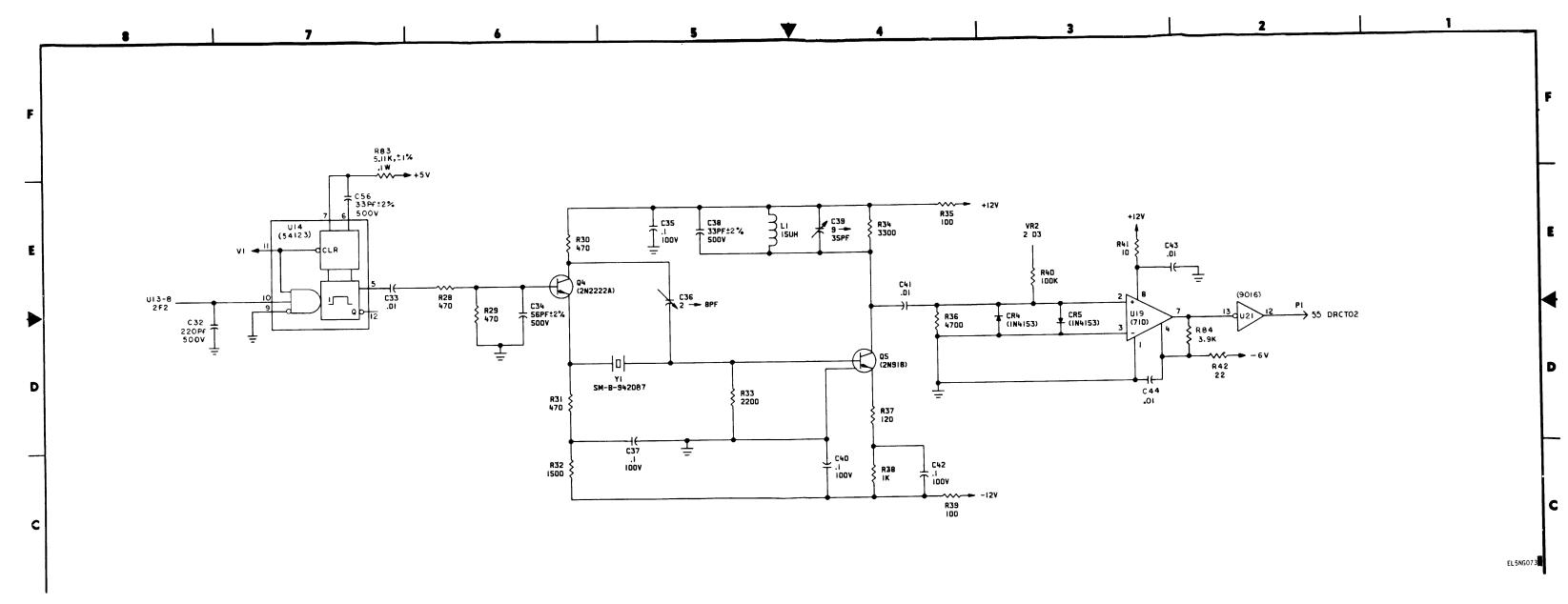

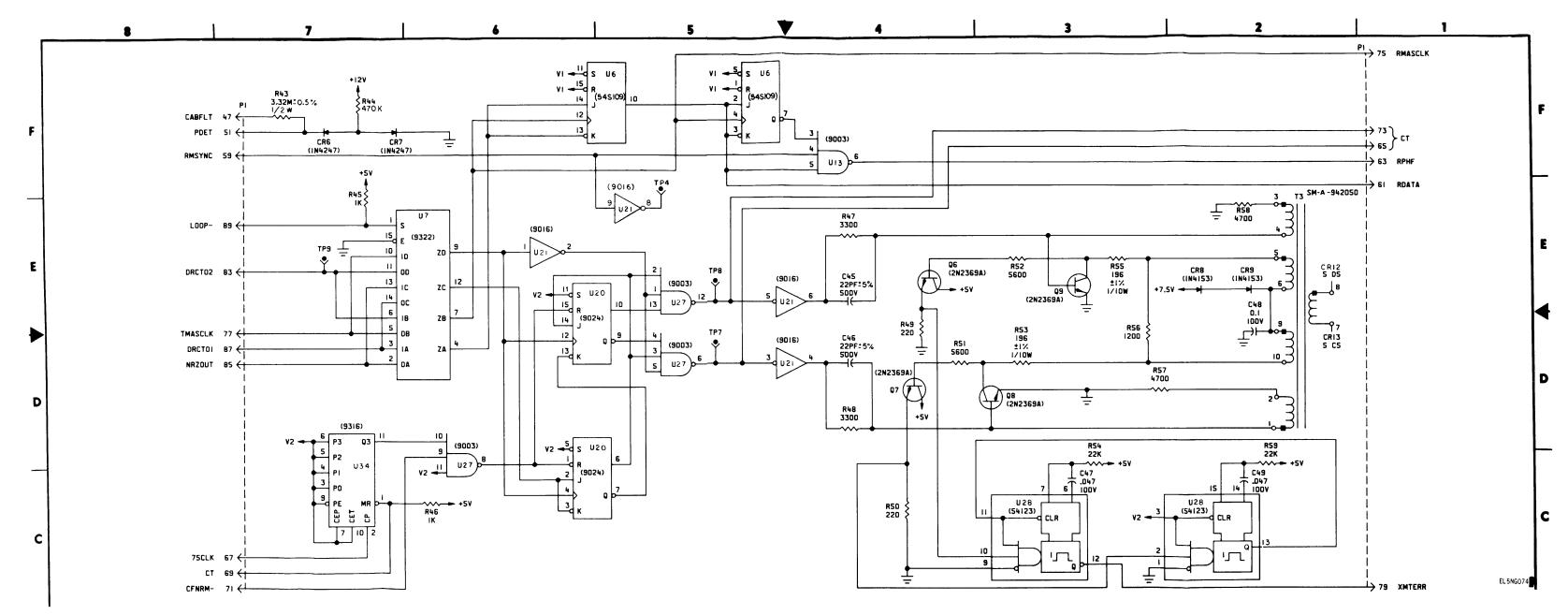

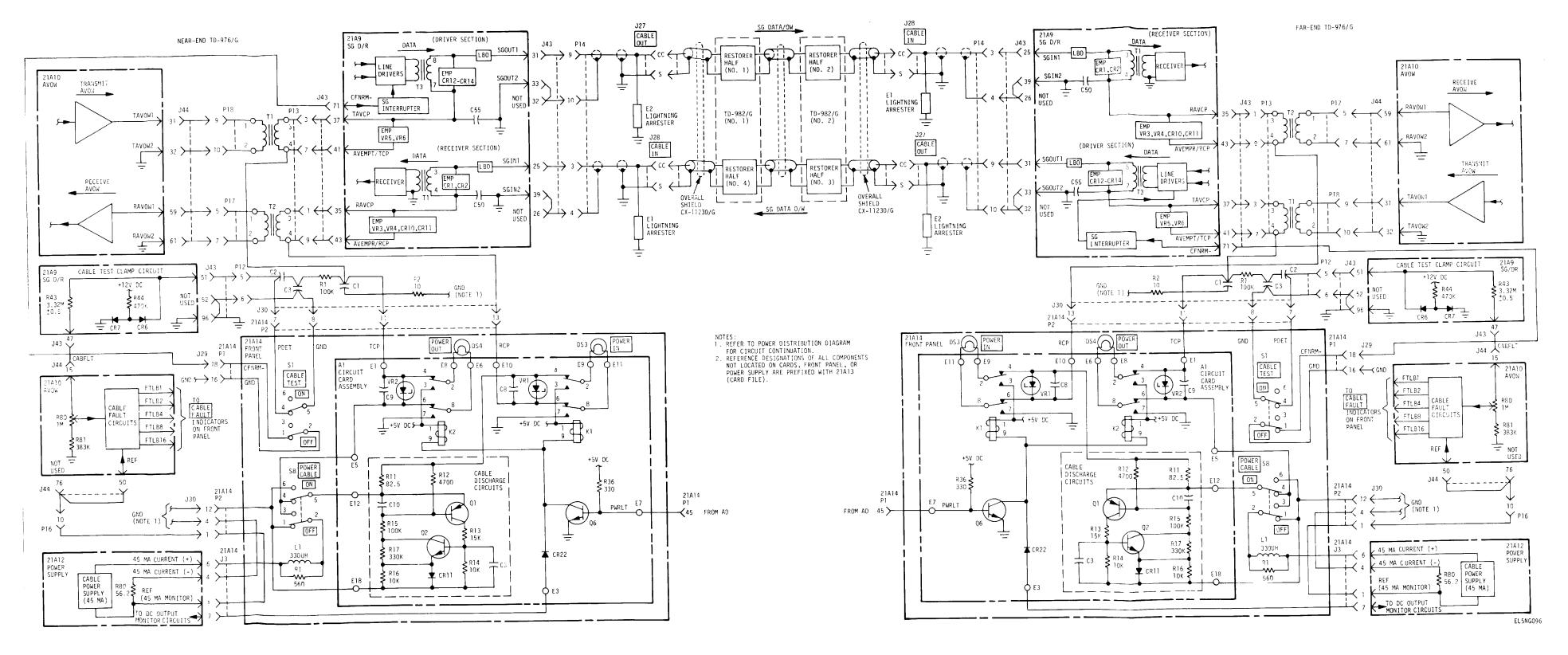

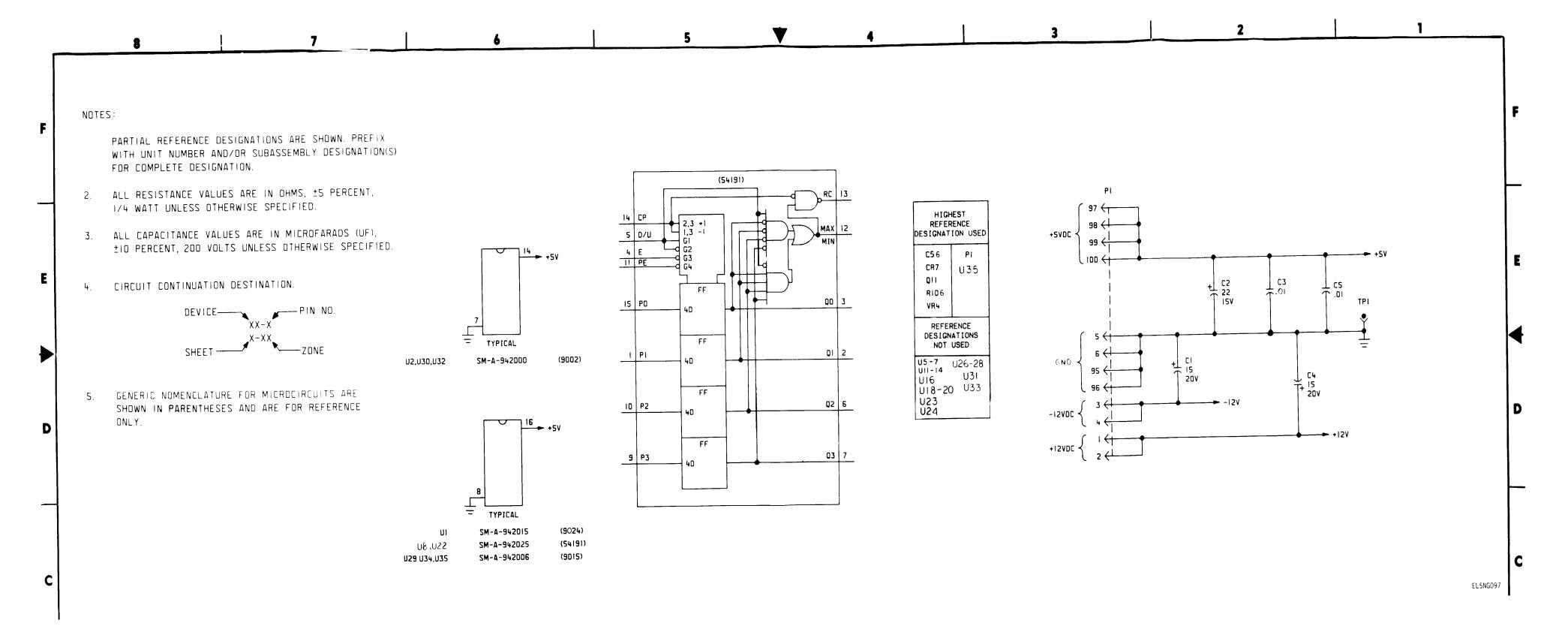

| FO-10            | SG D/R card 21A9, schematic diagram (5 sheet)                                         | *           |

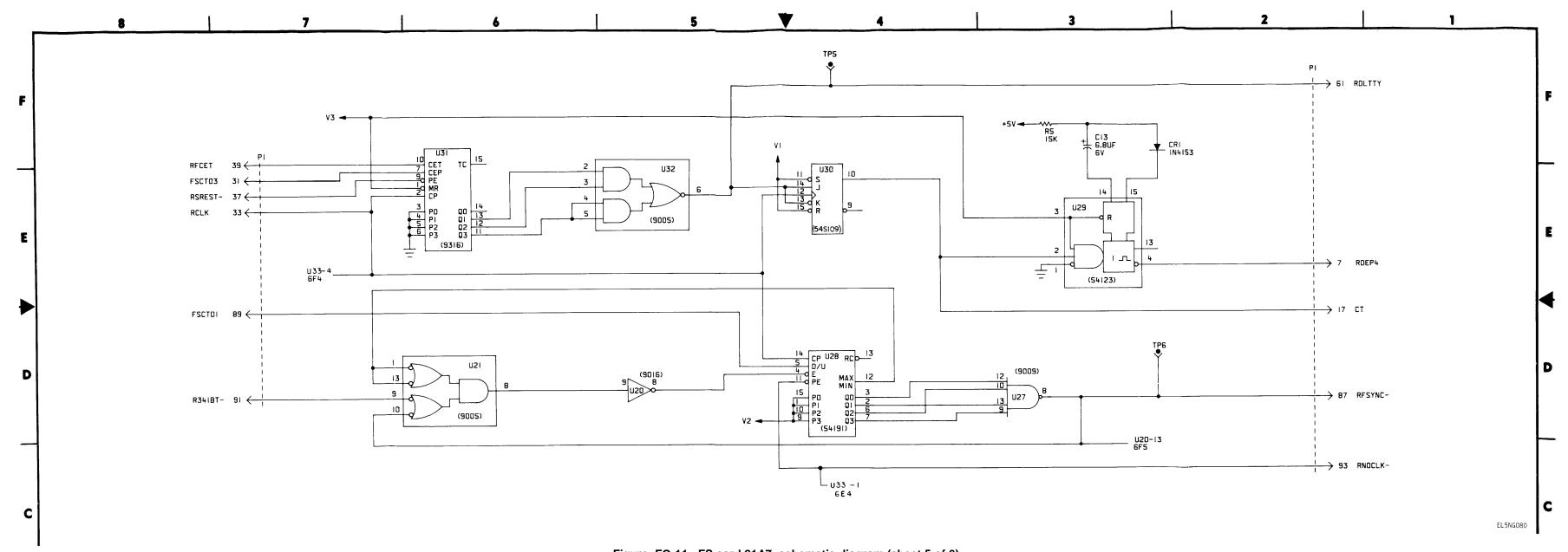

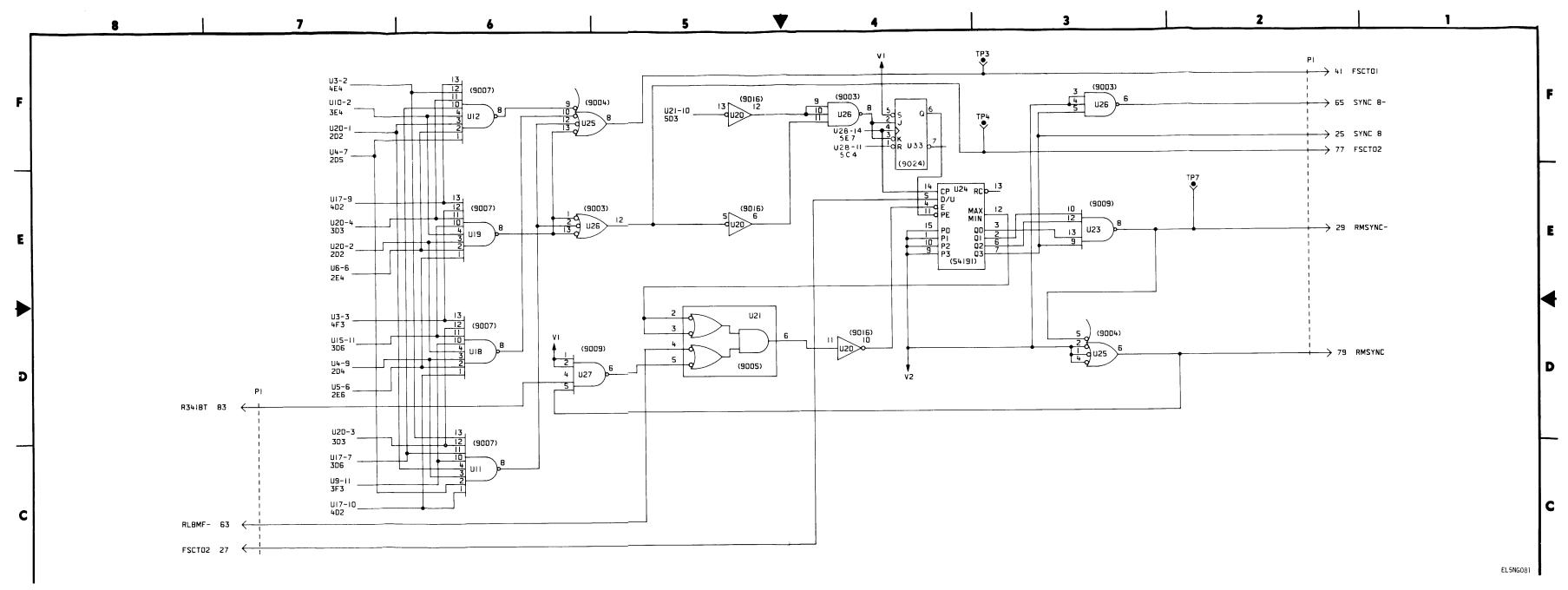

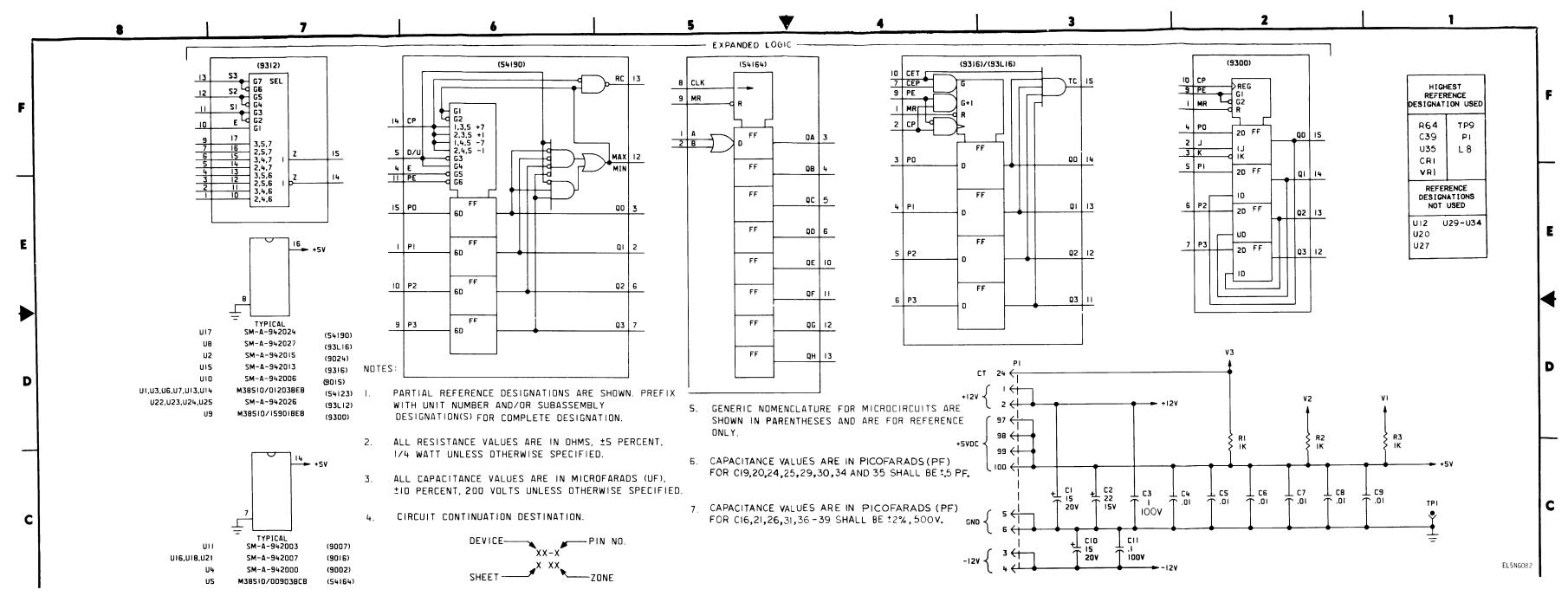

| FO-11            | FS card 21A7, schematic diagram (6 sees)                                              | *           |

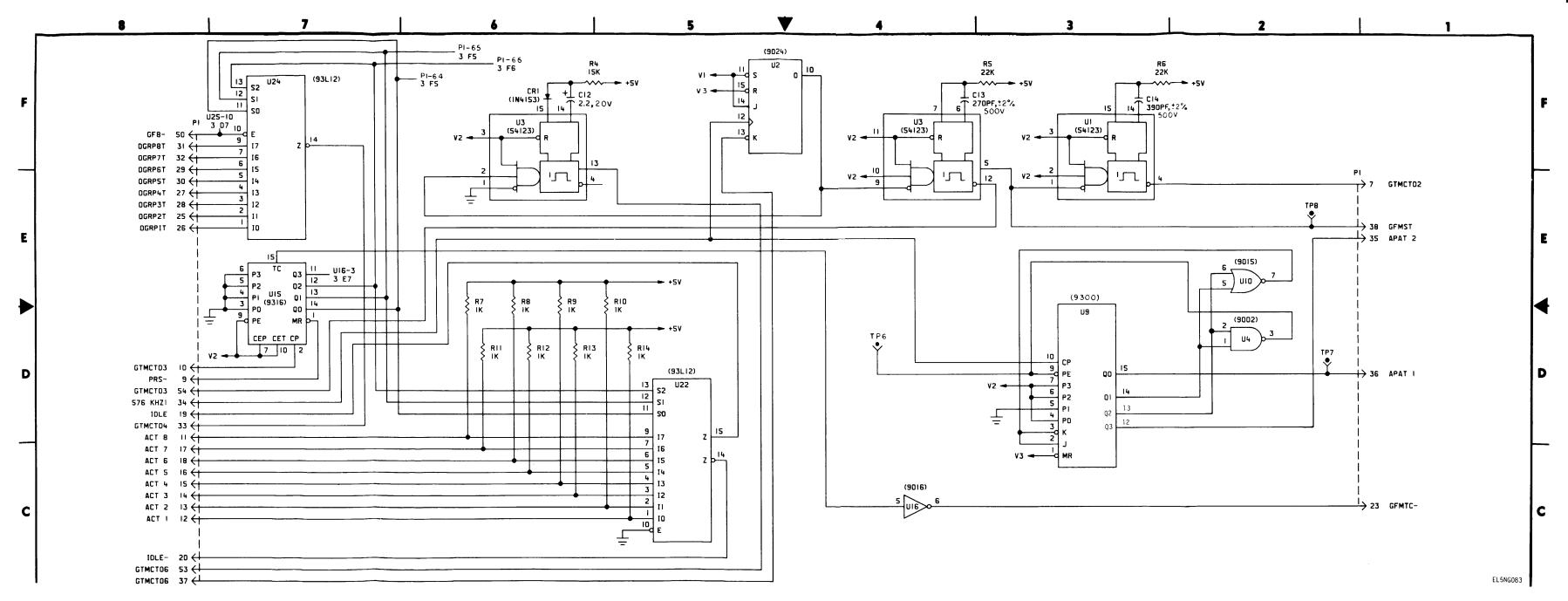

| FO-12            | GTM card 21A2, schematic diagram (5 sheets)                                           | *           |

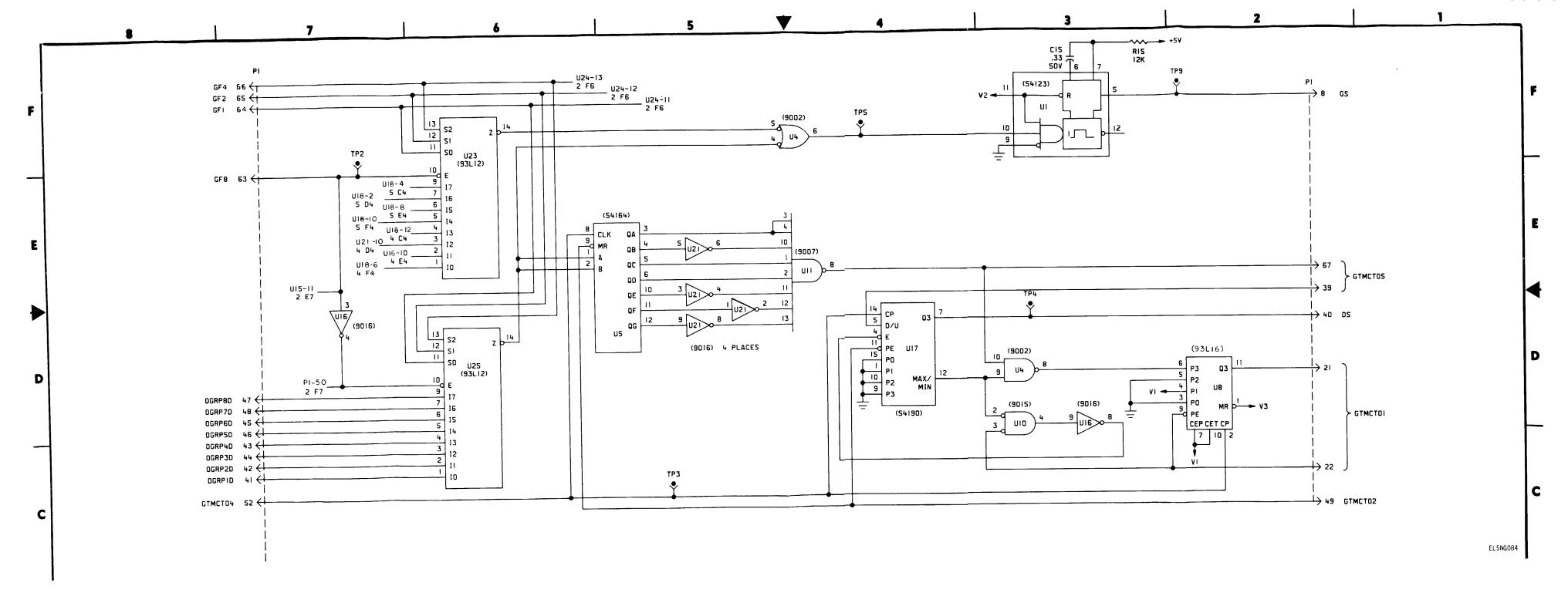

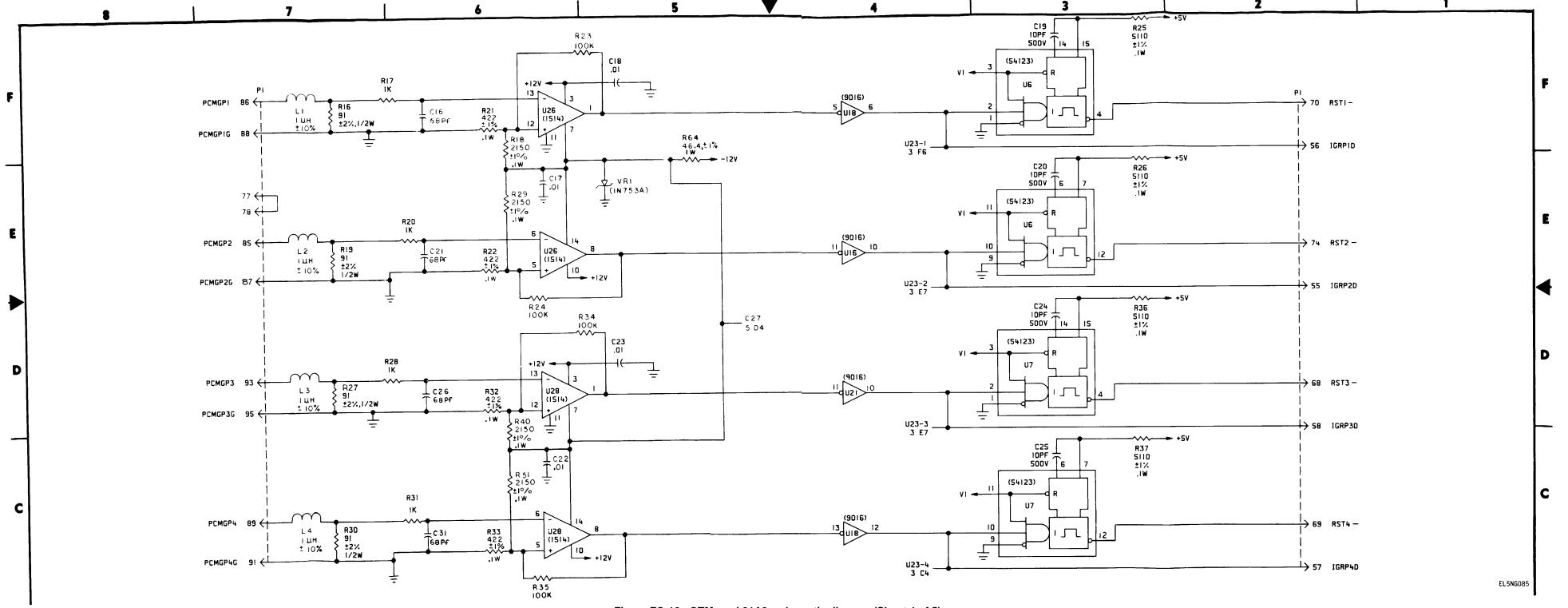

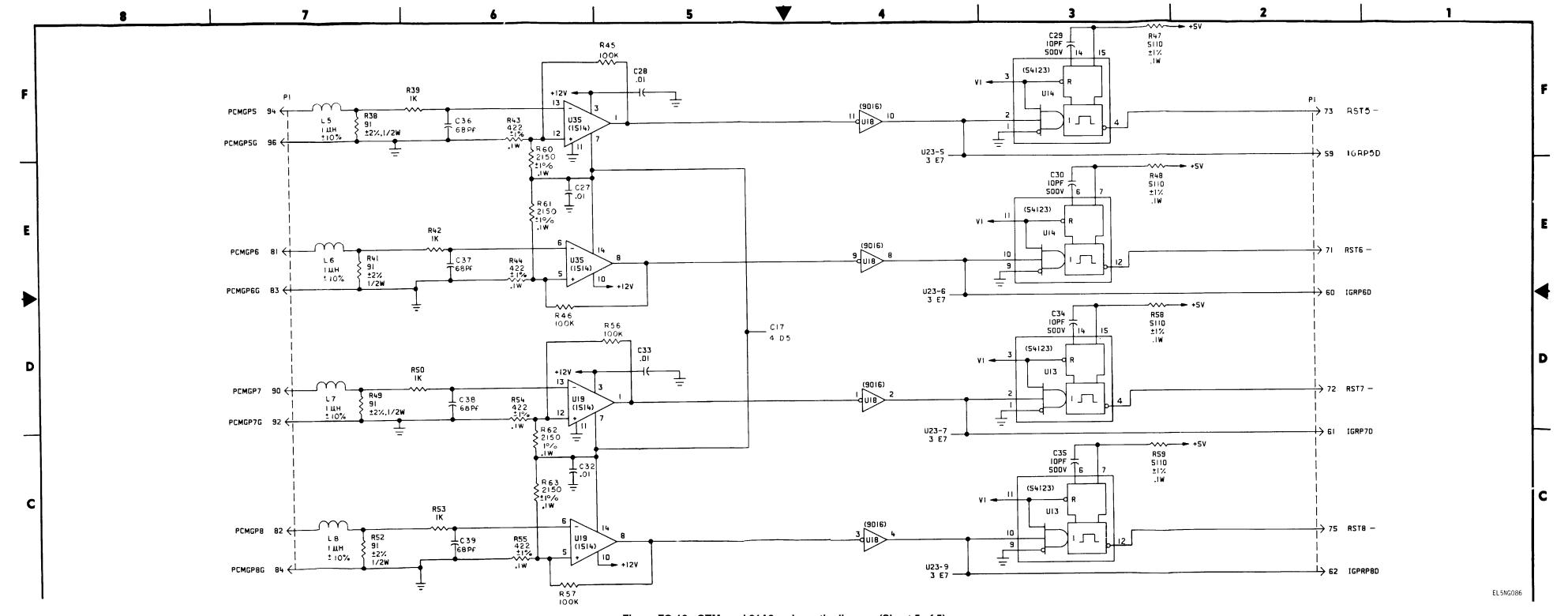

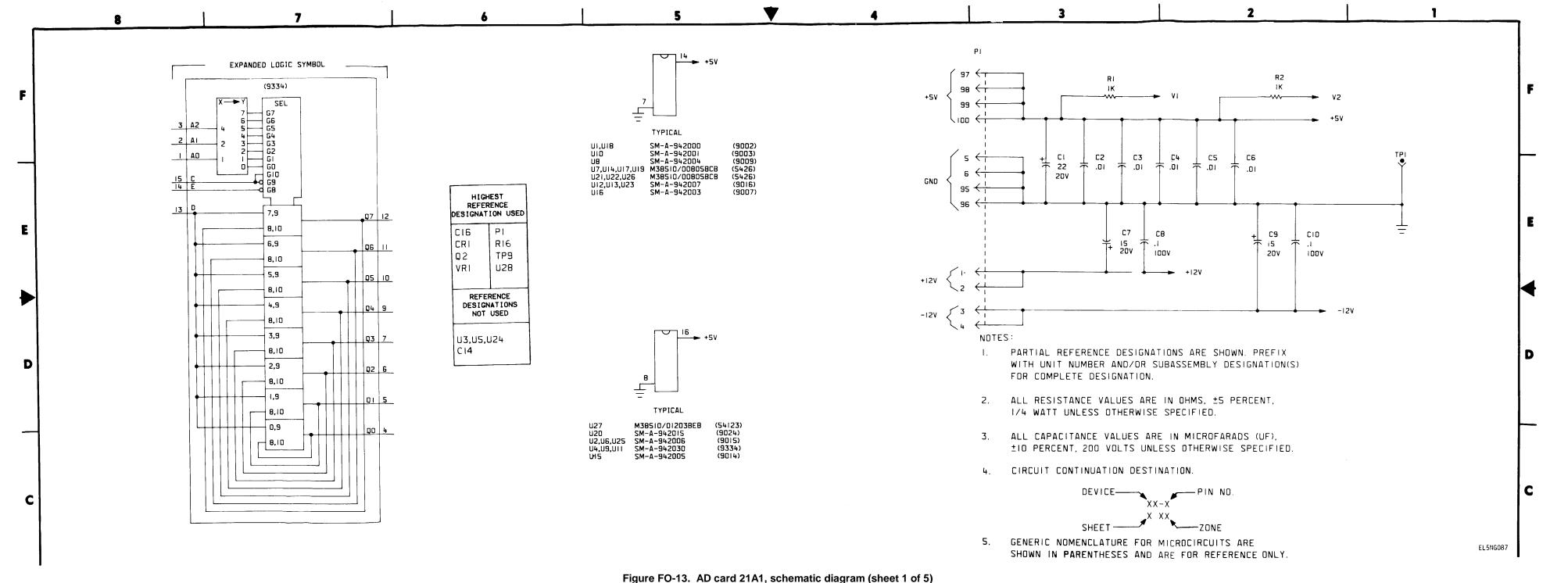

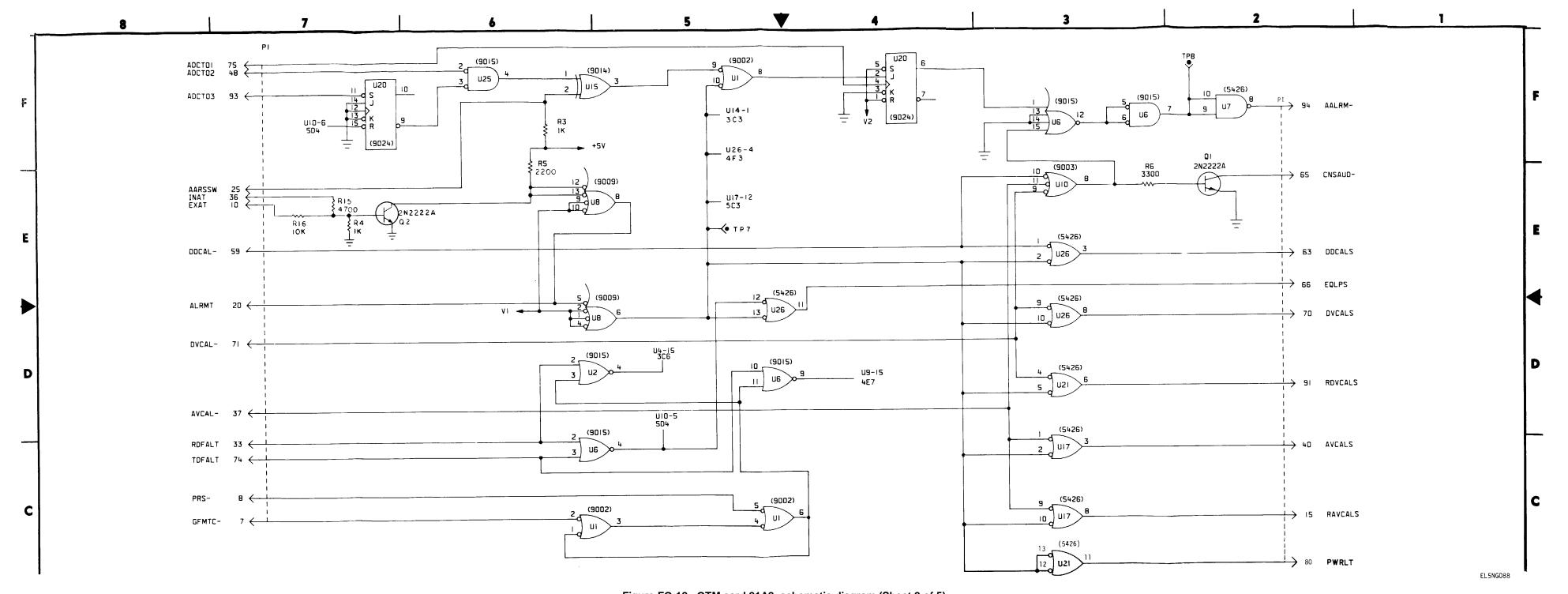

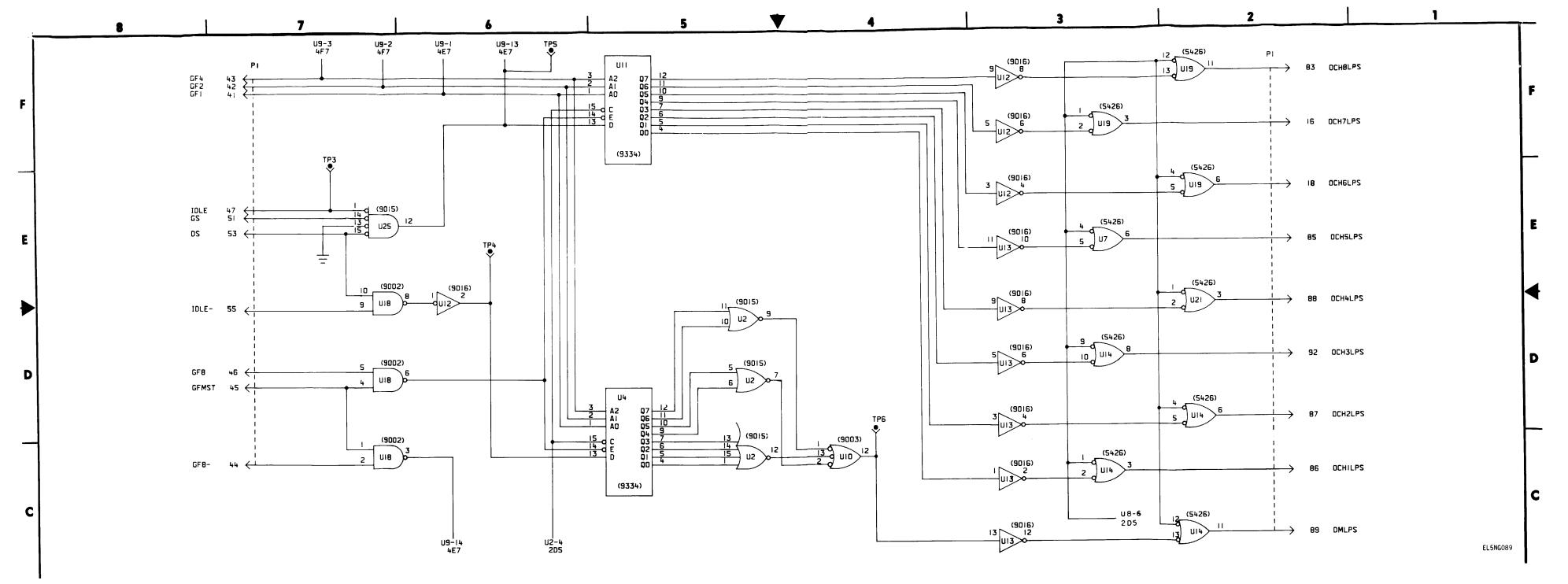

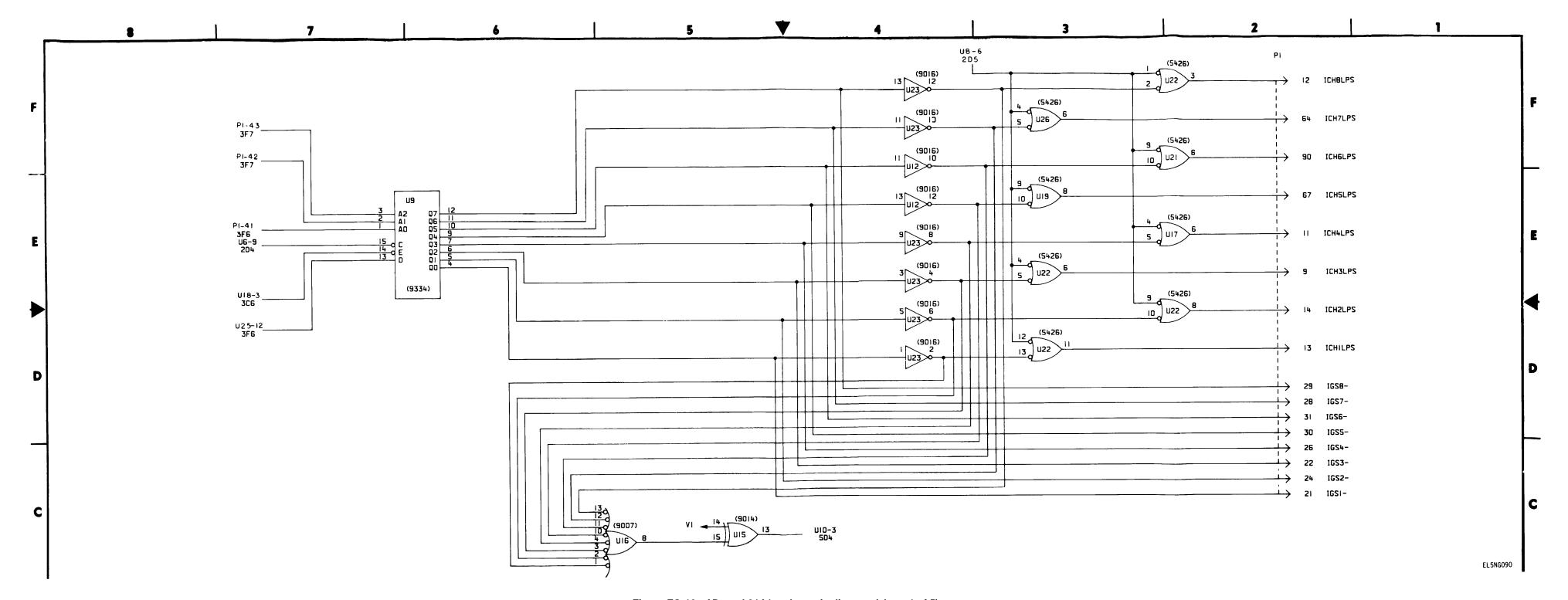

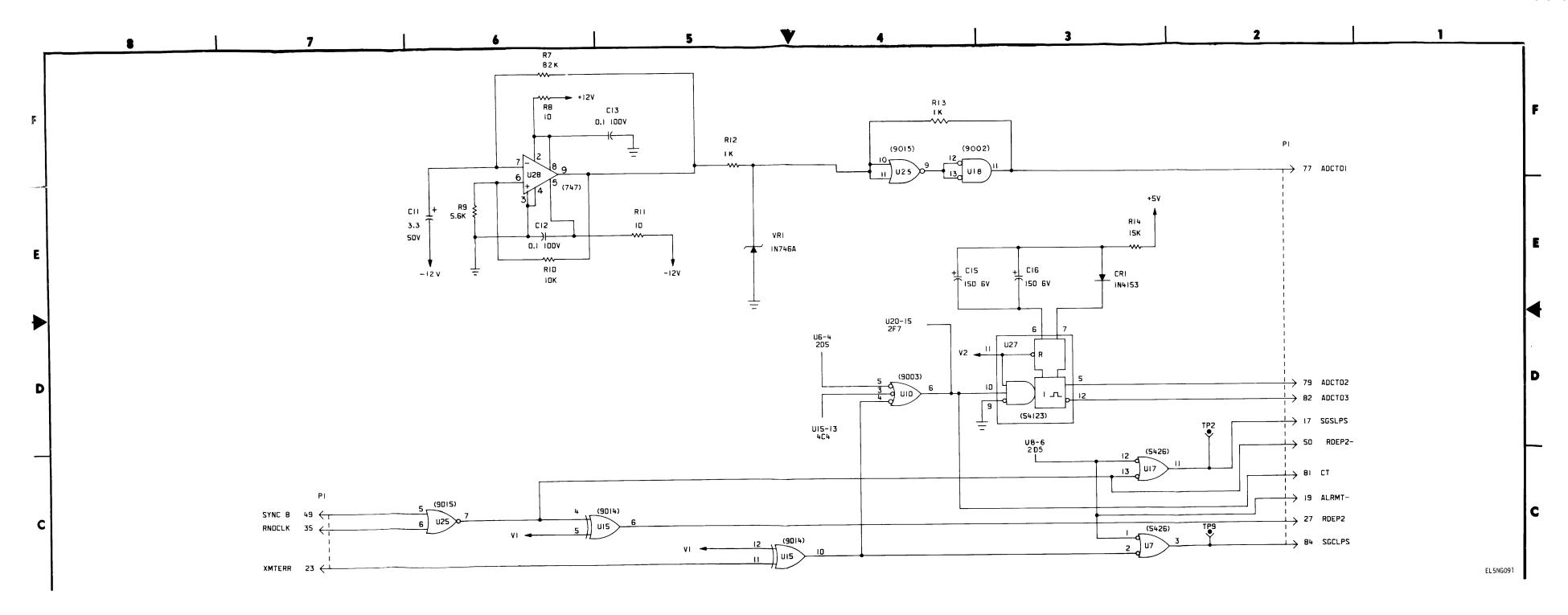

| FO-13            | AD card 21Al, schematic diagram (5 sheets)                                            | *           |

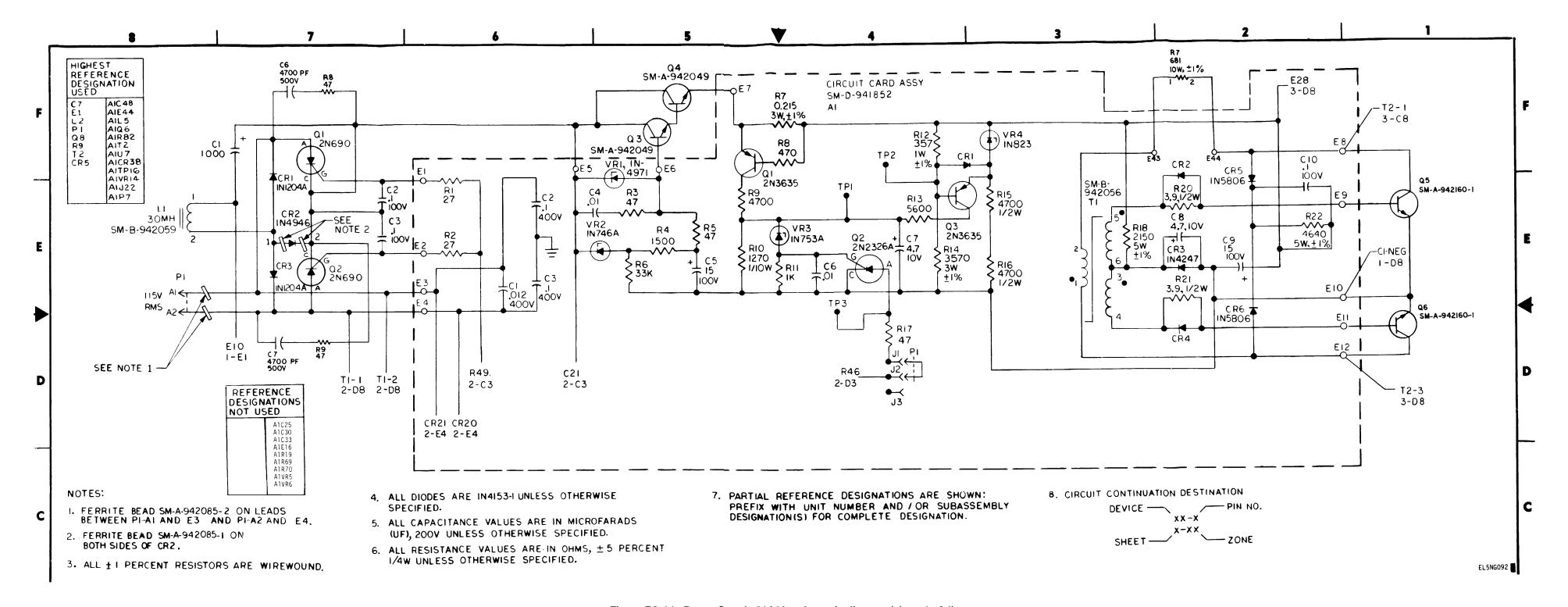

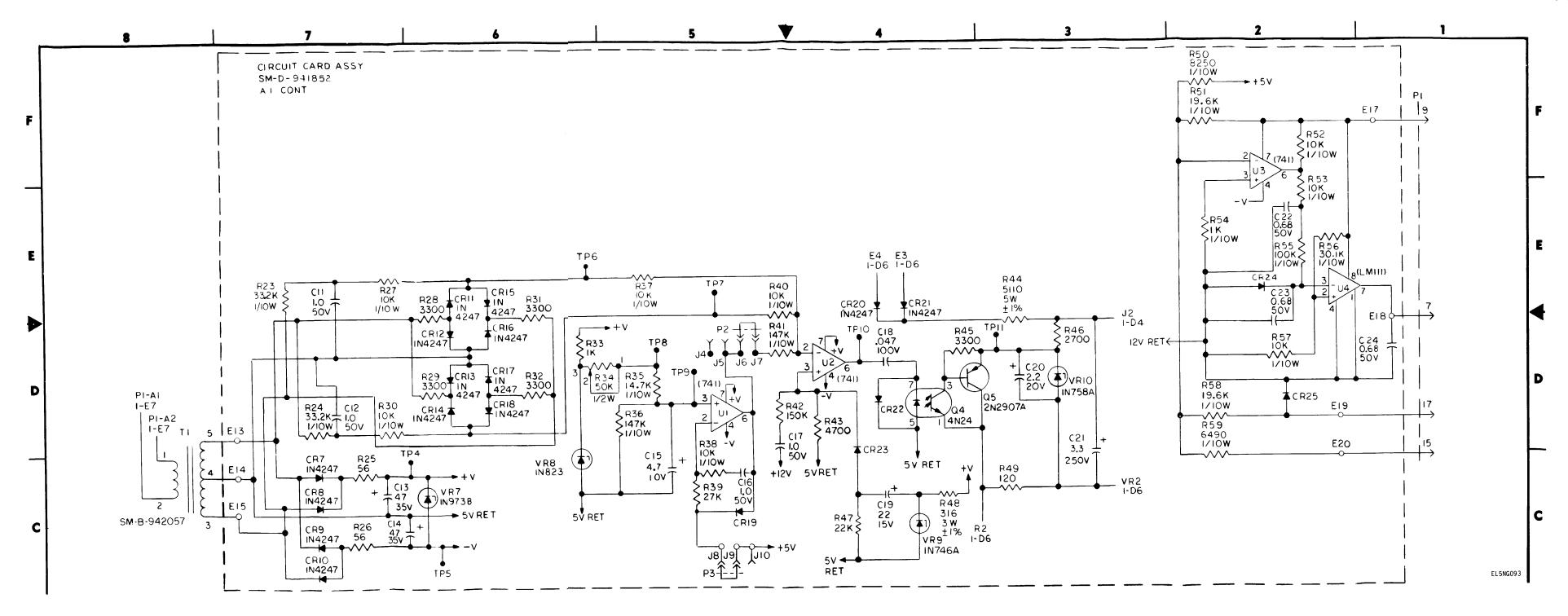

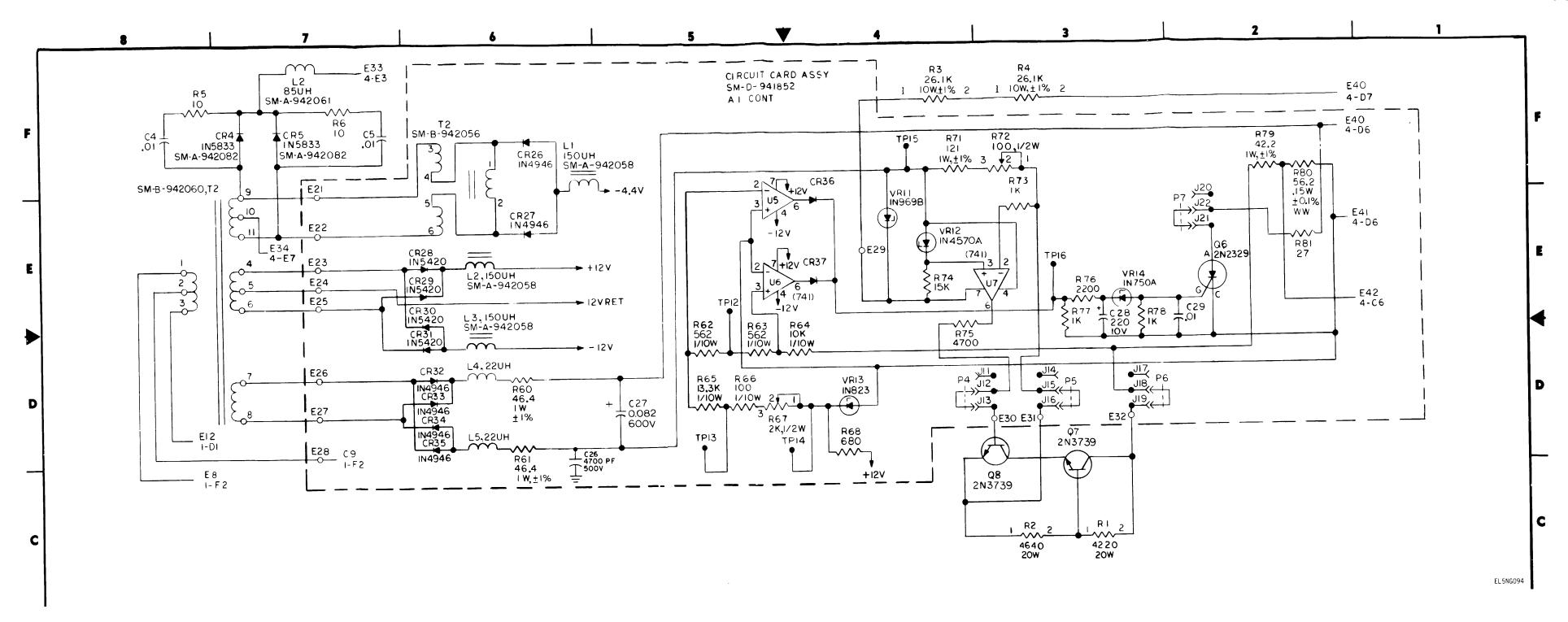

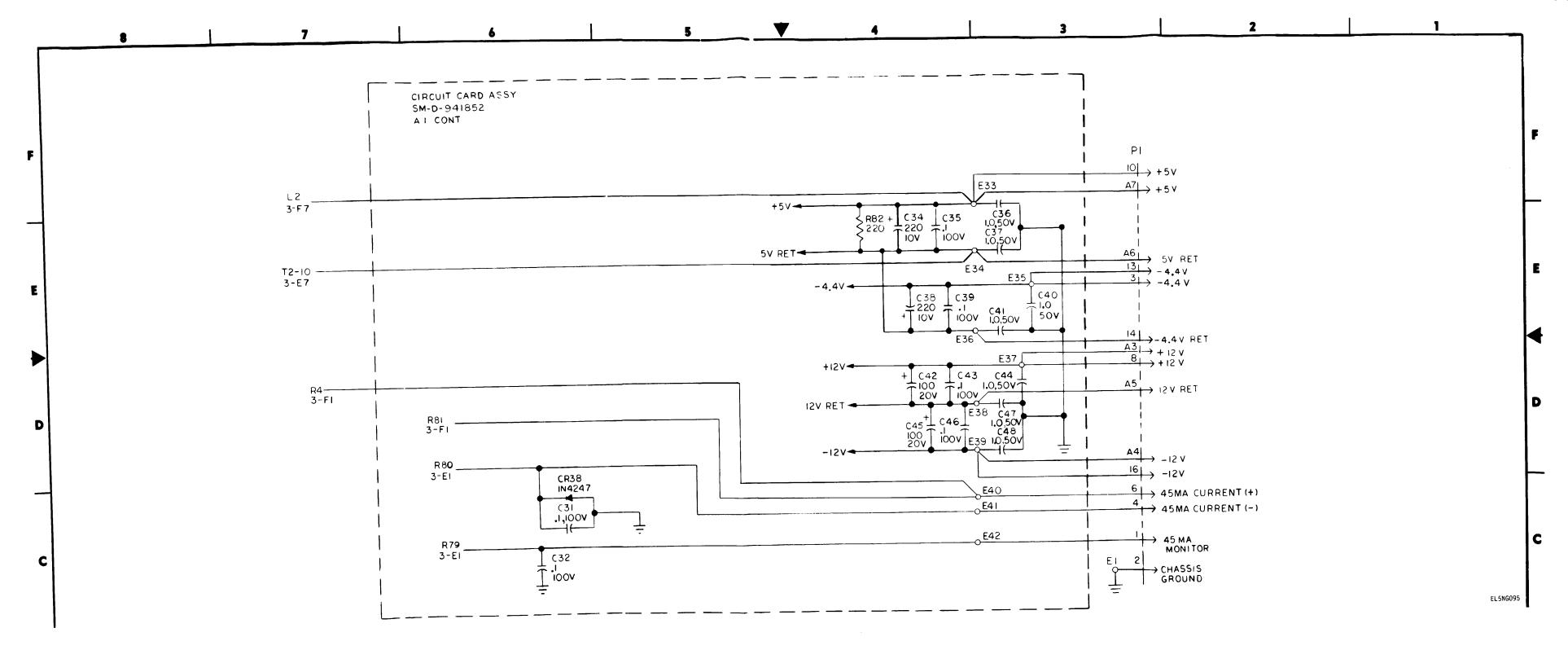

| FO-14            | Power supply 21A12, schematic diagram (4 sheets)                                      | *           |

| FO-15            | Typical cable system interfaces                                                       | *           |

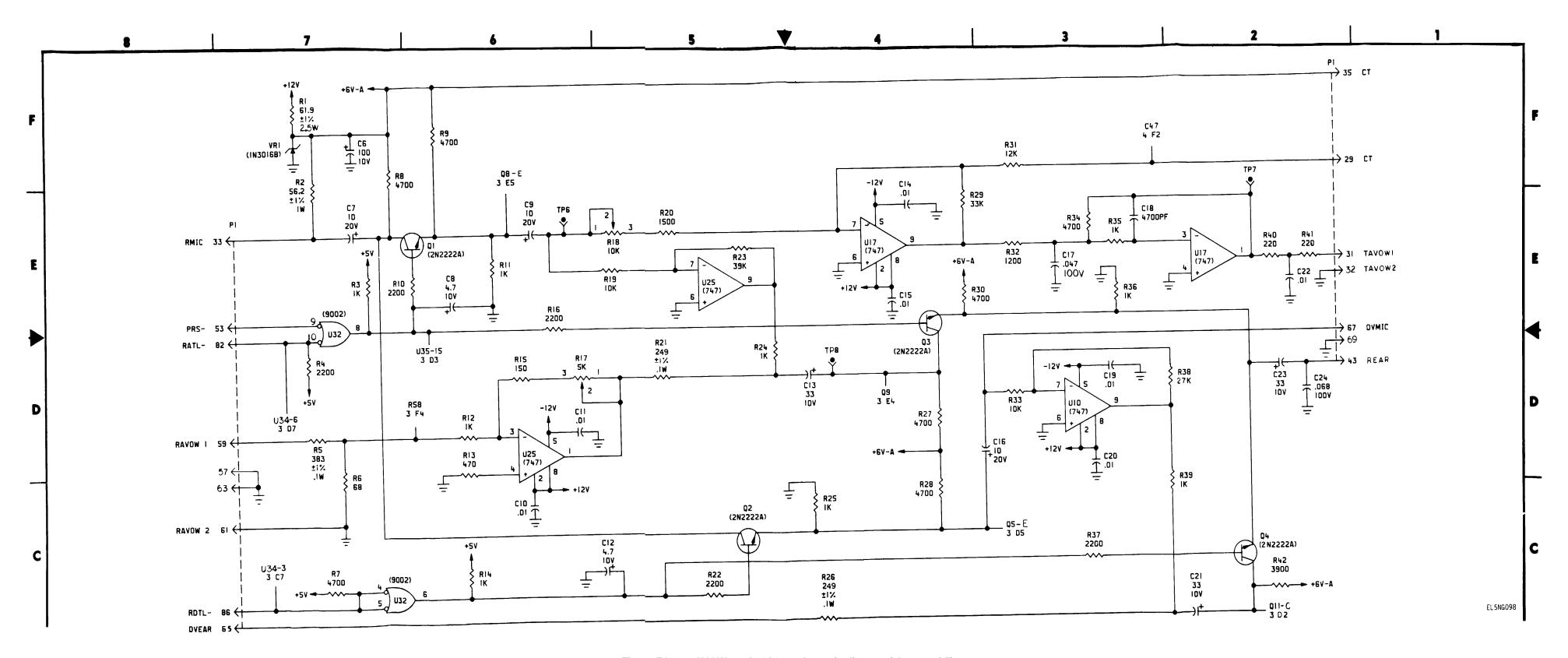

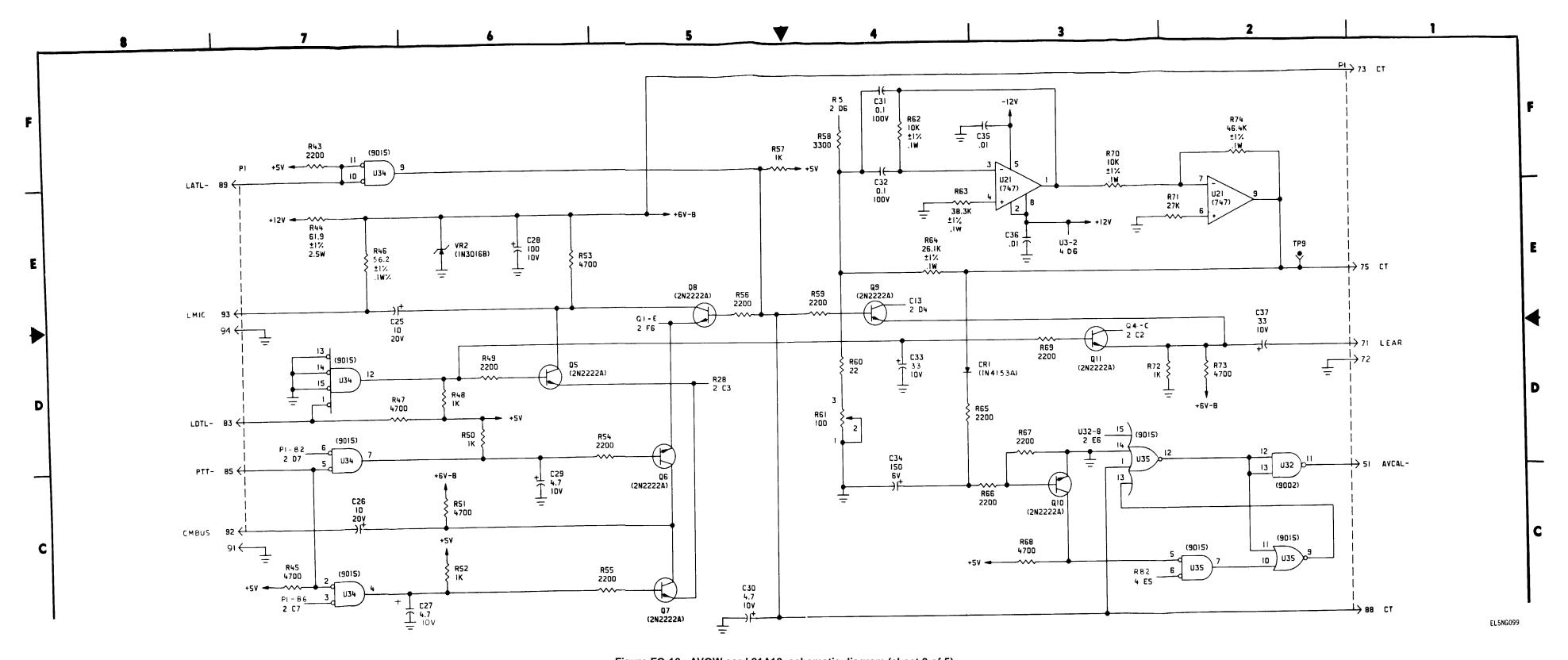

| FO-16            | AVOW card 21A10, schematic diagram (5 sheets)                                         | *           |

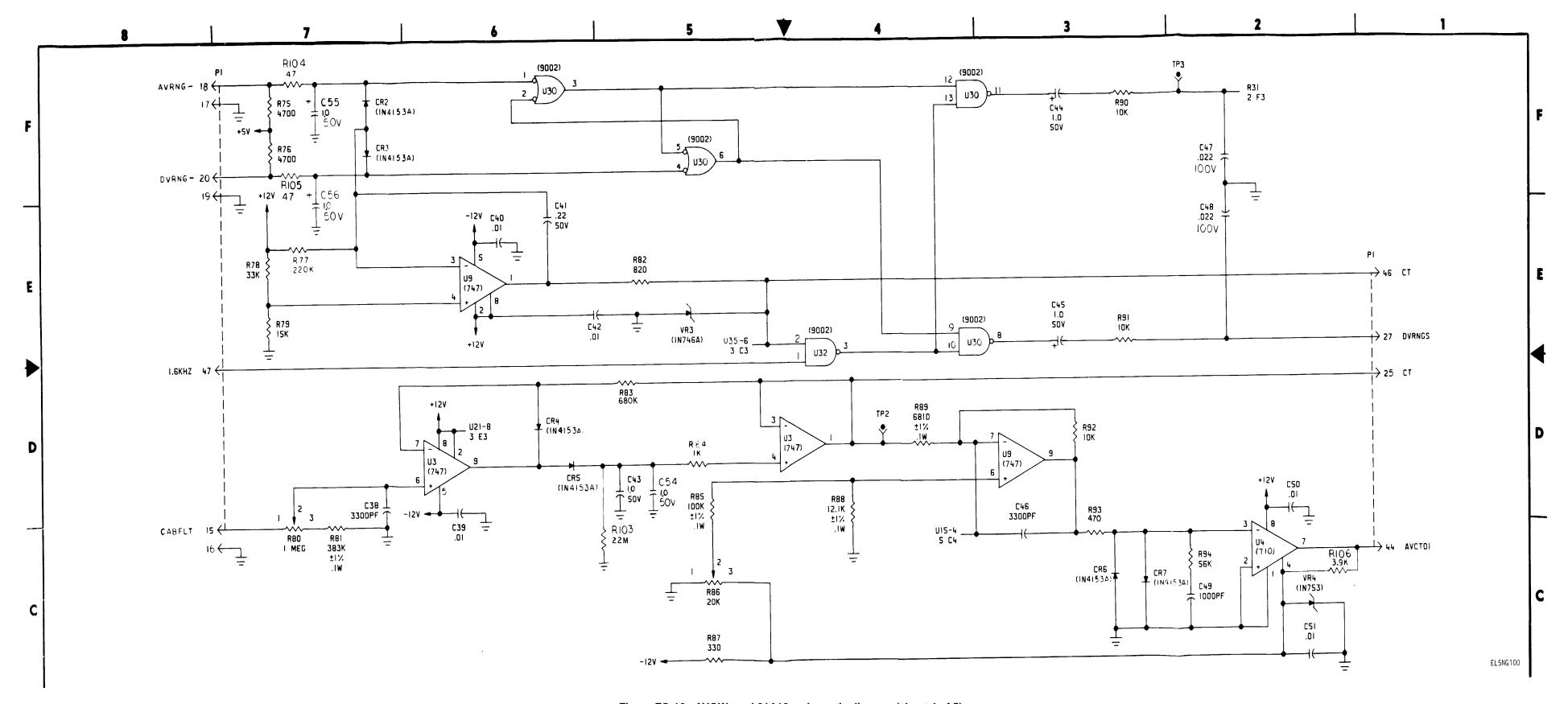

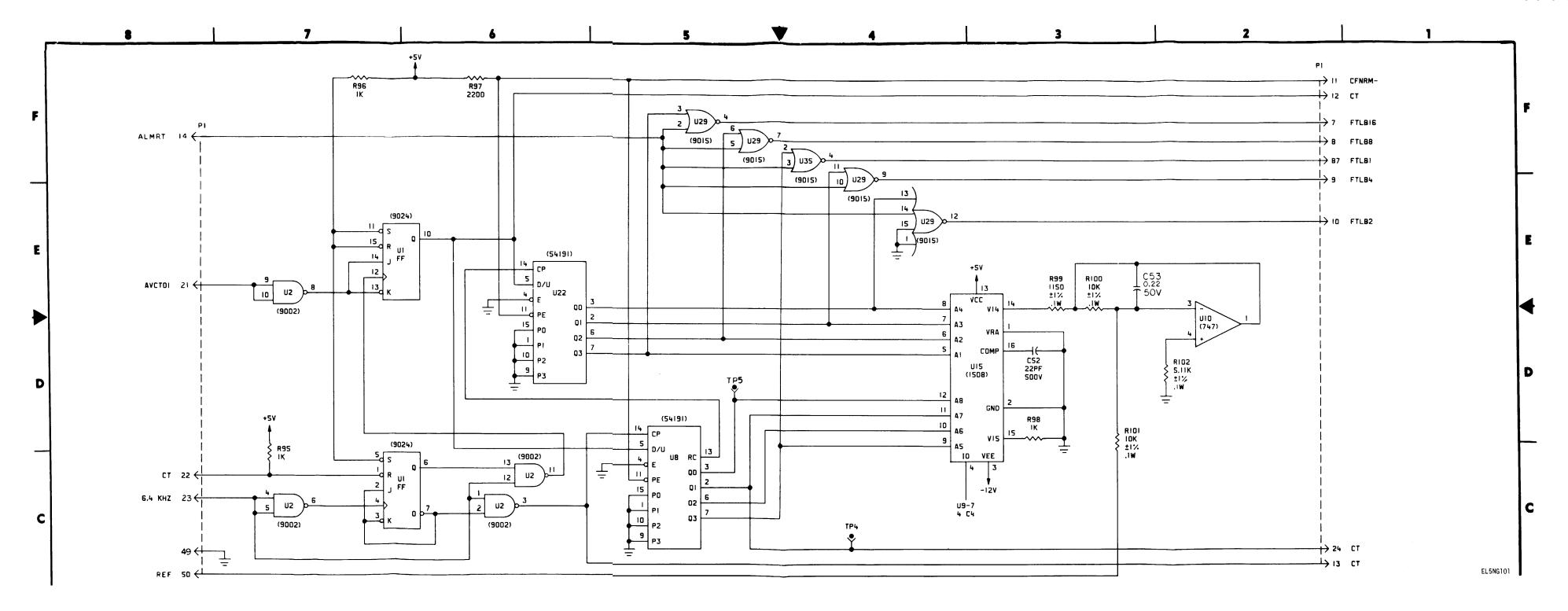

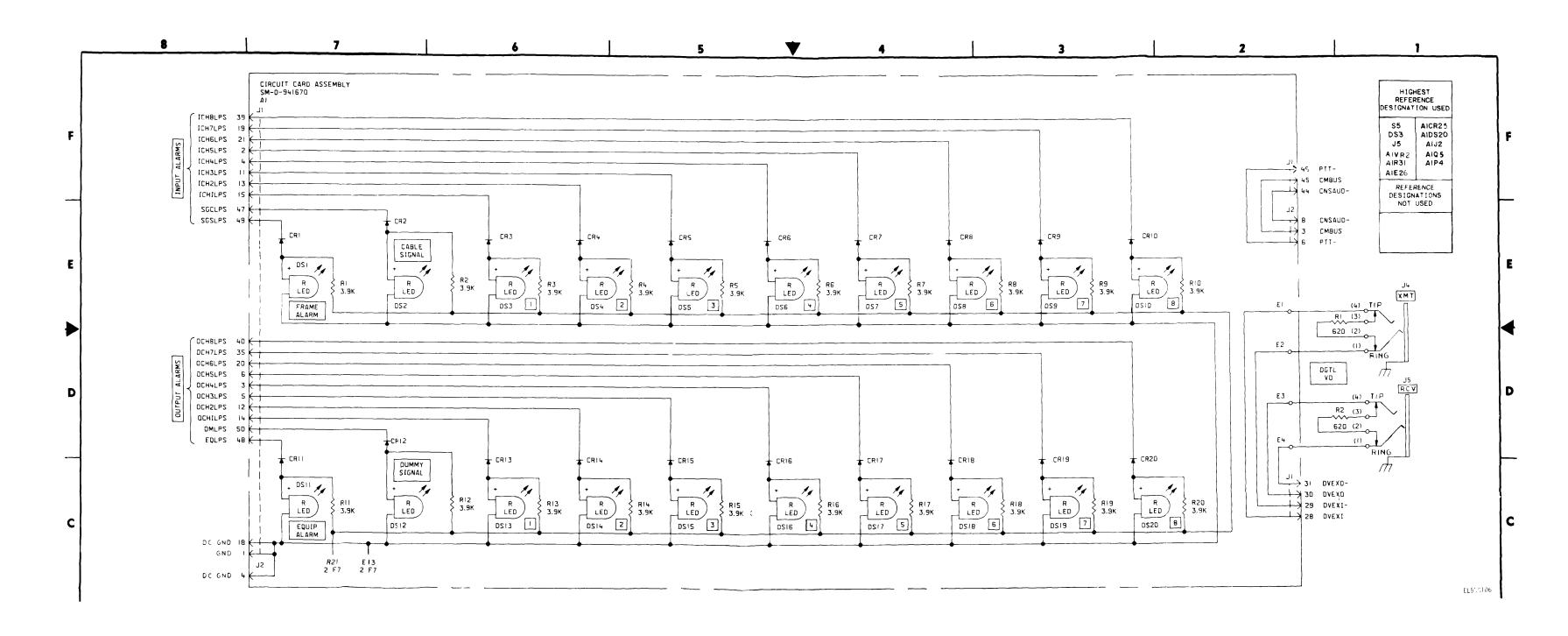

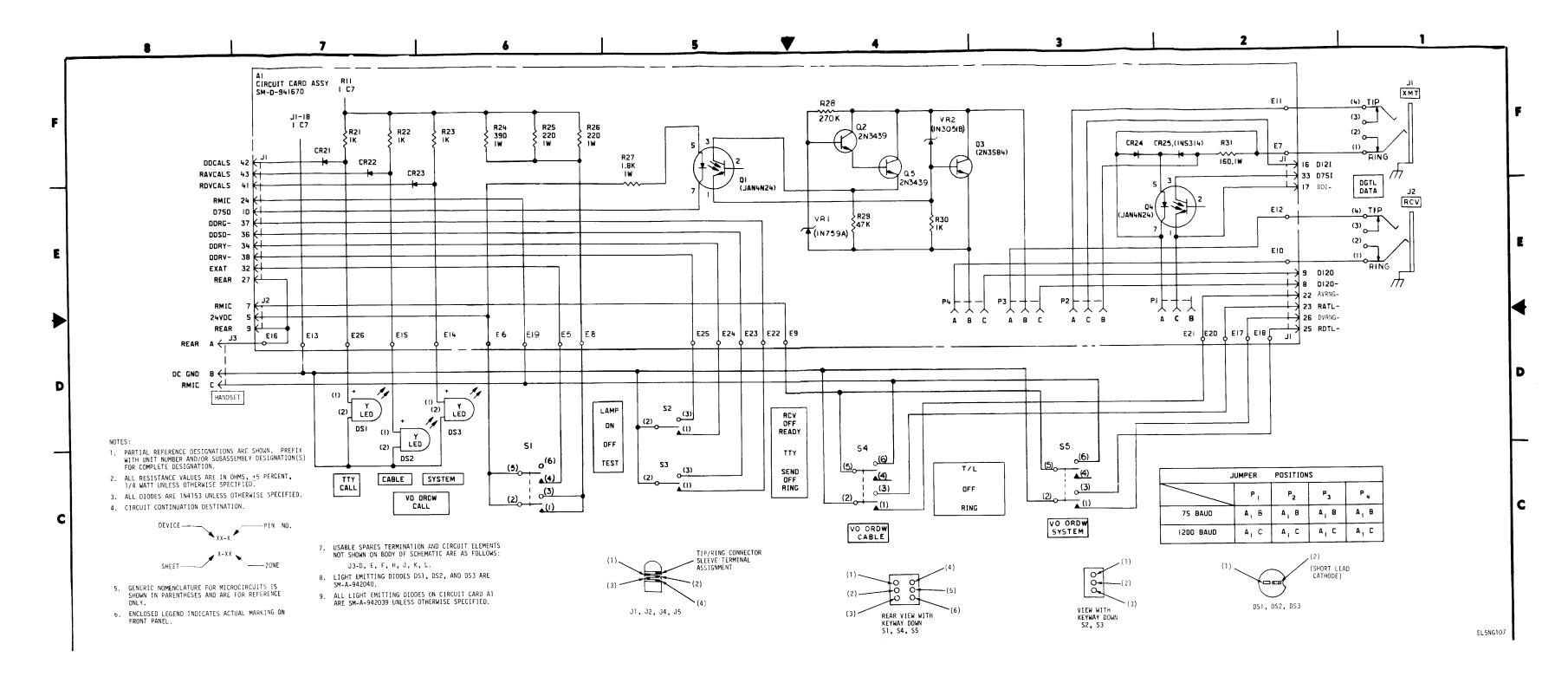

| FO-17            | Front panel 21A14, schematic diagram (2 sheets)                                       | *           |

| FO-18            | Front panel circuit card 21A14A1, schematic diagram (2 sheets)                        | *           |

| FO-19            | RAU 21A15, schematic diagram (2 sheets)                                               | *           |

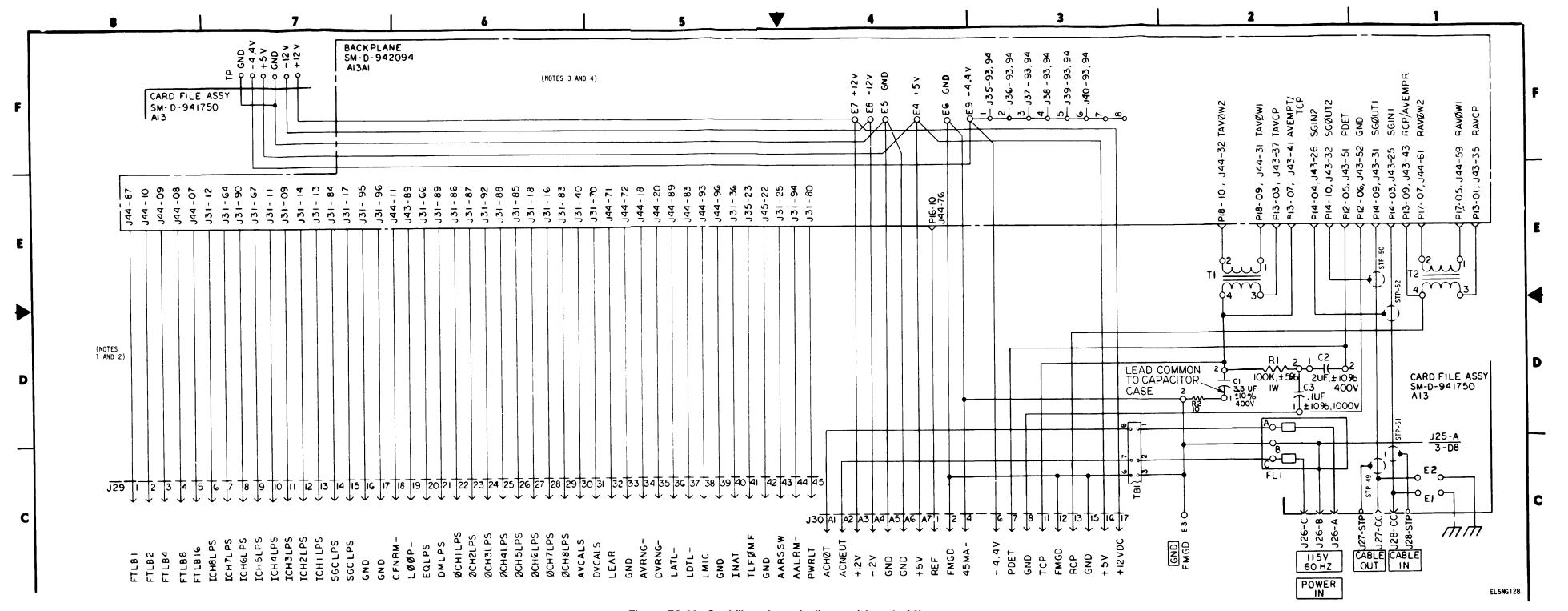

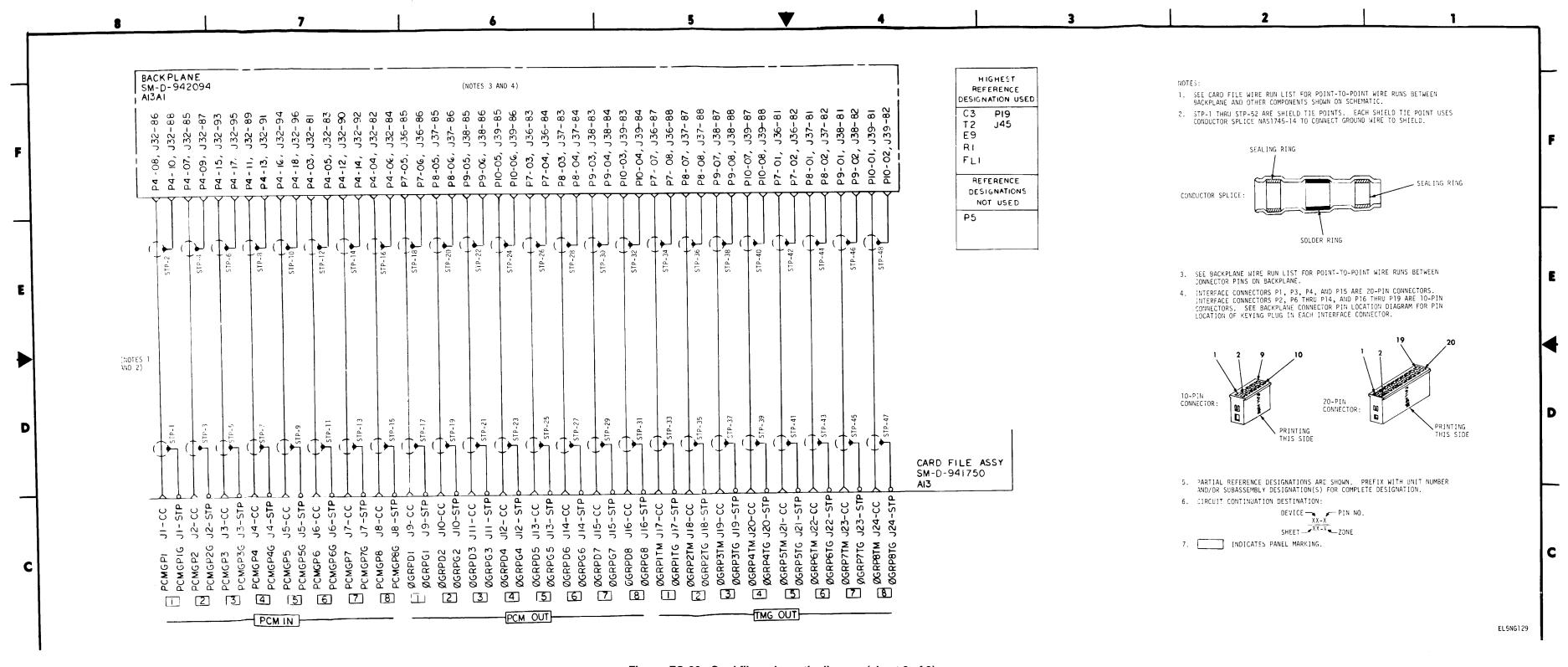

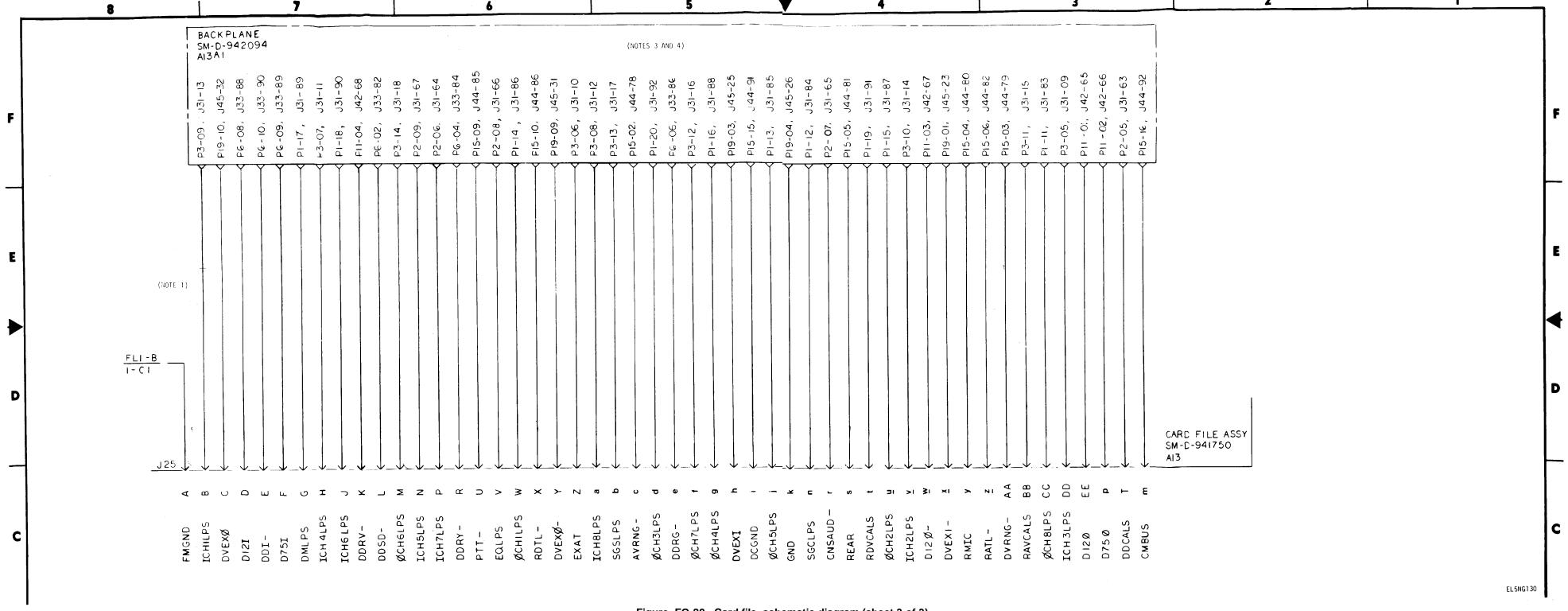

| FO-20            | Card file, schematic diagram (3 sheets)                                               | *           |

|                  | d-in page, located in the back of the manual.                                         |             |

| , , , , ,        | The page, results in the page, of the manual                                          |             |

|                  | LIST OF TABLES                                                                        |             |

| Number           | Title                                                                                 | Page        |

| 1-1              | Reference Designations and Common Names                                               | 1-2         |

| 1-2              | Signal Names and Definitions                                                          | 1-2         |

| 2-1              | GateU21-6EnableTimes                                                                  | 2-35        |

| 2-2              | Minor Frame Decoder Inputs and Outputs                                                | 2-36        |

| 2-3              | Stuff Code Generator Operating Logic Levels                                           | 2-37        |

| 2-4              | Input Selector U2 Operating Conditions                                                | 2-45        |

| 2-5              | Output Selector U17 Operating Conditions                                              | 2-47        |

| 3-1              | Direct Support Test Equipment Lit                                                     | 3-3         |

| 3-2              | Direct Support Tools List                                                             | 3-4         |

| 3-3              | Tools and Test Equipment Required for TD-976/G Visual Inspections and Test Procedures | 3-7         |

| 3-4              | TD-976/G Inspection Procedures                                                        | 3-7         |

| 3-5              | Test Equipment Required for Power Supply Output Test                                  | 3-8         |

| 3-6              | Power Supply Output Test                                                              | 3-9         |

| 3-7              | Test Equipment Required for Alarm and Indicator Lamp Test                             | 3-10        |

| 3-8              | Alarm and Indicator Lamp Test                                                         | 3-11        |

| 3-9              | Test Equipment Required for Data Transfer Test                                        | 3-13        |

| 3-10             | Data Transfer Test                                                                    | 3-13        |

| 3-11             | rest Equipment Required for AVOW Test                                                 | 3-18        |

| 3-12             | AVOW Test                                                                             | 3-19        |

| - · <del>-</del> |                                                                                       | 3 10        |

iii

# TM 11-7025-202-34

| Number | Title                                                    | Page   |

|--------|----------------------------------------------------------|--------|

| 3-13   | Test Equipment Required for DVOW Test                    | 3-22   |

| 3-14   | DVOW Test                                                | 3-22   |

| 3-15   | Test Equipment Required for Cable Fault Detection Test   | 3-25   |

| 3-16   | -Cable Fault Detection Test                              | 3-25   |

| 3-17   | Test Equipment Required for DDOW Test                    | 3-26   |

| 3-18   | DDOW Test                                                | 3-27   |

| 3-19   | Power Supply Output Test Troubleshooting Chart           | 3-31   |

| 3-20   | Alarm and Indicator Lamp Test Troubleshooting Chart      | 3-32   |

| 3-21   | Data Transfer Test Troubleshooting Chart                 | 3-33   |

| 3-22   | AVOW Test Troubleshooting Chart                          | 3-34   |

| 3-23   | DVOW Test Troubleshooting Chart                          | 3-36   |

| 3-24   | Cable Fault Detection Test Troubleshooting Chart         | 3-38   |

| 3-25   | DDOW Test Troubleshooting Chart                          | 3-39   |

| 3-26   | Test Equipment Required for RAU Test and Troubleshooting | 3-41   |

| 3-27   | RAU Test and Troubleshooting                             | 3-41   |

| 3-28   | Locking Clip Housing Data                                | 3-75   |

| 3-29   | RAU Wire Run List                                        | 3-82   |

| 3-30   | Front Panel Wire Run List                                | 3-83   |

| 3-31   | Card File Wire Run List                                  | 3-85   |

| 3-32   | Card File Backplane Wire Run List                        | 3-88   |

| 3-33   | Cable Marker Sleeve Marking Information                  | 3-95   |

| 4-1    | General Support Tools and Test Equipment List            | 4-2    |

| 4-2    | Power Supply Inspection Procedures                       | 4-2    |

| 4-3    | Test Equipment Required for Power Supply Tests           | 4-3    |

| 4-4    | Power Supply Test Procedures                             | 4-7    |

| 4-5    | Test Equipment Required for Power Supply Troubleshooting | 4-10   |

| 4-6    | DC Power Supply Circuits Troubleshooting Procedures      | 4-11   |

| 4-7    | Cable Power Supply Circuits Troubleshooting Procedures   | 4-16   |

| 4-8    | Heat Sink Transistor Resistance Checks                   | 4-23   |

| 4-9    | Power Supply Wire Run List                               | 4-24   |

| 4-10   | Tools Required for Power Supply Repair                   | 4-24.1 |

# NOTE

The Remote Access Unit (RAU), 21A15, and the Digital Data Orderwire Printed Circuit Board, 21A8, have been removed from the TD-976/G; they are no longer required. Any reference or illustration of these items or of their associated equipment such as RAU Feedthru Box or the RAU Breakout Box within this technical manual must be disregarded.

CHANGE 2 1-0

#### **CHAPTER 1**

#### INTRODUCTION

# Section I. GENERAL

# 1-1. Scope

- a. This manual contains functional descriptions and direct support and general support maintenance instructions for Multiplexer TD-976/G (hereafter referred to as the TD-976/G). Chapter 2 contains functional descriptions of the equipment. Chapters 3 and 4 contain detailed direct support and general maintenance instructions.

- b. Sections I through III of chapter 2 contain general discussions of the TD-9761G interfaces, the supergroup (SG) message formats, and the basic equipment concepts. Section IV of chapter 2 is devoted to an overall block diagram discussion of the TD-976/G. Additional sections of chapter 2 contain detailed block diagram and logic/schematic discussions for each plugin printed circuit card and the power supply.

- c. The direct support maintenance instructions in chapter 3 consist of detailed testing, troubleshooting, and performance tests for the overall TD-976/G, the front panel, and the remote access unit (RAU). Also, maintenance instructions for repair of the assemblies that make up the TD-976/G, less the plug-in printed circuit cards, are included in chapter 3. Detailed troubleshooting and repair of the plug-in printed circuit cards is a depot level function and instructions are contained in DMWR 11-7025-202. The general support maintenance instructions in chapter 4 consist of detailed testing, troubleshooting, and performance tests for the

power supply. Also, maintenance instructions for repair of the power supply are included in chapter 4.

#### 1-2. Maintenance Forms and Records

Department of the Army forms and procedures used for equipment maintenance will be those prescribed in TM 38750.

# 1-3. Destruction of Army Materiel To Prevent Enemy Use

Refer to TM 750-244-2 for procedures to be followed for destruction of materiel to prevent enemy use.

# 1-4. Administrative Storage

Refer to TM 740-90-1 for procedures, forms, records, and inspections required during administrative storage of the TD-976/G.

# 1-5. Reporting Equipment Improvement Recommendations (EIR's)

EIR's will be prepared using SF 368, Quality Deficiency Report, Maintenance Request. Instructions for preparing EIR's are provided in TM 38-750, The Army Maintenance Management System. EIR's should be mailed direct to Commander, US Army Communications and Electronics Materiel Readiness Command, ATTN: DRSEL-ME-MQ, Fort Monmouth, NJ 07703. A reply will be furnished direct to you.

## Section II. DESCRIPTION AND DATA

#### 1-6. Equipment Description

Physical descriptions and illustrations of the TD976/G are contained in TM 11-7025-202-12. Additional equipment descriptions and illustrations needed for direct support maintenance of the TD976/G are contained in chapter 3. General support maintenance information is contained in chapter 4.

#### 1-7. Tabulated Data

The operating characteristics and physical dimensions of the TD-9761G are contained in the tabulated data in TM 11-7025-202-12.

# 1-8. Common Names and Reference Designations

Common names and reference designations for major components of the TD-976/G are listed in table 1-1.

The plug-in printed circuit cards are assigned reference designations 21A1 through 21A11 (common multiple use plug-in cards are assigned the same reference designation). The common names listed in the "Common name" column of table 1-1 are the abbreviated names used throughout the manual for these items. The "Card connector" column lists the reference designation (J number) of each connector in the card file into which a printed circuit card is plugged

## 1-9. Common Terms

The common terms used in this manual in discussions

of various data handling functions are defined in the glossary.

#### 1-10. Signal Names

a. The functional signals used in the TD-976/G are assigned signal names in the form of mnemonic codes (in most cases, formed from initial letters or syllables of selected words) chosen to convey useful information. The signal names and their definitions are listed in table 1-2. Additionally, the card or assembly that generates the signal is listed in the "Source" column of table 1-2 while the card (or cards) and/or assembly (or

assemblies) to which the signal is applied are listed in the "Destination(s)" column.

- b. A bar (-) indicator appears at the end of selected signal names. When shown on a block or schematic diagram or in text, the bar indicator means that the negative (low) level of the signal is the true condition required for the specific logic function being performed.

- c. The mnemonic CT (card test) appears frequently at card input/output pins on the logic diagrams. These particular card pins are used only during card testing. Therefore, the mnemonic CT is not listed in table 1-2.

Table 1-1. Reference Designations and Common Names

| Reference   |                                      | Common        | Card      |

|-------------|--------------------------------------|---------------|-----------|

| designation | Item                                 | name          | connector |

| 21A1        | Alarm detector card.                 | AD.           | J31       |

| 21A2        | Group traffic monitor card.          | GTM.          | J32       |

| 21A3        | Digital data orderwire encoder card. | DDOW encoder. | J33       |

| 21A4        | Master oscillator/combiner card.     | MOIC.         | J34       |

| 21A5        | Timing and control card (mux).       | TC (M).       | J35       |

| 21A5        | Timing and control card (demux).     | TC (D).       | J40       |

| 21A6        | Dual group processor card No. 1.     | DGP No. 1.    | J36       |

| 21A6        | Dual group processor card No. 2.     | DGP No. 2.    | J37       |

| 21A6        | Dual group processor card No. 3.     | DGP No. 3.    | J38       |

| 21A6        | Dual group processor card No. 4.     | DGP No. 4.    | J39       |

| 21A7        | Frame sync card.                     | FS.           | J41       |

| 21A8        | Digital data orderwire decoder card. | DDOW decoder. | J42       |

| 21A9        | Supergroup driver/receiver card.     | SG DIR.       | J43       |

| 21A10       | Analog voice orderwire card.         | AVOW.         | J44       |

| 21A11       | Digital voice orderwire card.        | DVOW.         | J45       |

| 21A12       | Power supply.                        | Power supply. |           |

| 21A13       | Card file assembly.                  | Card file.    |           |

| 21A14       | Control panel assembly.              | Front panel.  |           |

| 21A15       | Remote access unit.                  | RAU.          |           |

**Table 1-2. Signal Names and Definitions**

| Signal     |                                     |              |                |

|------------|-------------------------------------|--------------|----------------|

| name       | Definition                          | Source       | Destination(s) |

|            |                                     |              |                |

| AALRM-     | Audible alarm.                      | AD.          | Front panel.   |

| AARSSW     | Audible alarm reset switch.         | Front panel. | AD.            |

| ACHOT      | Alternating current hot.            | AC input.    | Front panel.   |

| ACHOTO     | Alternating current hot output.     | Front panel. | Power supply.  |

| ACNEUT     | Alternating current neutral.        | AC input.    | Front panel.   |

| ACNEUTO    | Alternating current neutral output. | Front panel. | Power supply.  |

| ACT(CH A)  | (Refer to ACT 1 through ACT 4.)     |              |                |

| ACT (CH B) | (Refer to ACT 5 through ACT 8.)     |              |                |

| ACT 1      | Activity select group 1 (CH A).     | DGP No. 1.   | GTM.           |

| ACT 2      | Activity select group 2 (CH A).     | DGP No. 2.   | GTM.           |

| ACT 3      | Activity select group 3 (CH A).     | DGP No. 3.   | GTM.           |

| ACT 4      | Activity select group 4 (CH A).     | DGP No. 4.   | GTM.           |

| ACT 5      | Activity select group 5 (CH B).     | DGP No. 1.   | GTM.           |

| ACT 6      | Activity select group 6 (CH B).     | DGP No. 2.   | GTM.           |

| ACT 7      | Activity select group 7 (CH B).     | DGP No. 3.   | GTM.           |

| ACT 8      | Activity select group 8 (CH B).     | DGP No. 4.   | GTM.           |

| ADCT01     | AD card test loop 1.                | .1           |                |

| ADCT02     | AD card test loop 2.                | 1            |                |

| ADCT03     | AD card test loop 3.                | 1            | 1              |

| ALRMT      | Alarm test.                         | AD.          | AVOW.          |

See footnotes at end of table.

| Signal name  APAT 1  APAT2  AVCAIL AVCALS AVCT01 AVEMPR AVEMPT AVRNG-CABFLT CFNRM-CHAN CMBUS | Table 1-2. Signal Names and Definition  Definition  Activity pattern 1.  Activity pattern 2.  Analog voice call.  Analog voice call signal.  AVOW card test loop 1.  Analog voice EMP receive.  Analog voice EMP transmit.  Analog voice ring.  Cable fault.  Channel sleek (4000 kHz) | Source GTM. GTM. AVOW. AD 21A13T2. SG DIR. SG D/R. Front panel. | Destination(s)  DGP No. 1. DGP No. 3. DGP No. 2. DGP No. 4. AD. Front panel SG DIR. 21A13T1. AVOW. AVOW. |

|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| APAT2  AVCAIL  AVCALS  AVCT01  AVEMPR  AVEMPT  AVRNG-  CABFLT  CFNRM-                        | Activity pattern 2.  Analog voice call. Analog voice call signal. AVOW card test loop 1. Analog voice EMP receive. Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                      | GTM.  AVOW. AD 21A13T2. SG DIR.  SG D/R.                        | DGP No. 3. DGP No. 2. DGP No. 4. AD. Front panel1 SG DIR. 21A13T1. AVOW. AVOW.                           |

| AVCAIL AVCALS AVCT01 AVEMPR AVEMPT AVRNG- CABFLT CFNRM-                                      | Analog voice call. Analog voice call signal. AVOW card test loop 1. Analog voice EMP receive. Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                                           | AVOW. AD1 21A13T2. SG DIR. SG D/R.                              | DGP No. 2.<br>DGP No. 4.<br>AD.<br>Front panel.<br><sup>1</sup><br>SG DIR.<br>21A13T1.<br>AVOW.<br>AVOW. |

| AVCAIL AVCALS AVCT01 AVEMPR AVEMPT AVRNG- CABFLT CFNRM-                                      | Analog voice call. Analog voice call signal. AVOW card test loop 1. Analog voice EMP receive. Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                                           | AVOW. AD1 21A13T2. SG DIR. SG D/R.                              | DGP No. 4. AD. Front panel1 SG DIR. 21A13T1. AVOW. AVOW.                                                 |

| AVCALS AVCT01 AVEMPR AVEMPT AVRNG- CABFLT CFNRM-                                             | Analog voice call signal.  AVOW card test loop 1.  Analog voice EMP receive.  Analog voice EMP transmit.  Analog voice ring.  Cable fault.  Cable fault normal.                                                                                                                        | AD.<br>1<br>21A13T2.<br>SG DIR.<br>SG D/R.                      | AD. Front panel1 SG DIR. 21A13T1. AVOW. AVOW.                                                            |

| AVCALS AVCT01 AVEMPR AVEMPT AVRNG- CABFLT CFNRM-                                             | Analog voice call signal.  AVOW card test loop 1.  Analog voice EMP receive.  Analog voice EMP transmit.  Analog voice ring.  Cable fault.  Cable fault normal.                                                                                                                        | AD.<br>1<br>21A13T2.<br>SG DIR.<br>SG D/R.                      | Front panel1 SG DIR. 21A13T1. AVOW. AVOW.                                                                |

| AVCT01 AVEMPR AVEMPT AVRNG- CABFLT CFNRM-                                                    | AVOW card test loop 1. Analog voice EMP receive. Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                                                                                        | 1<br>21A13T2.<br>SG DIR.<br>SG D/R.                             | 1<br>SG DIR.<br>21A13T1.<br>AVOW.<br>AVOW.                                                               |

| AVEMPR<br>AVEMPT<br>AVRNG-<br>CABFLT<br>CFNRM-                                               | Analog voice EMP receive. Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                                                                                                               | 21A13T2.<br>SG DIR.<br>SG D/R.                                  | 21A13T1.<br>AVOW.<br>AVOW.                                                                               |

| AVEMPT<br>AVRNG-<br>CABFLT<br>CFNRM-<br>CHAN                                                 | Analog voice EMP transmit. Analog voice ring. Cable fault. Cable fault normal.                                                                                                                                                                                                         | SG D/R.                                                         | 21A13T1.<br>AVOW.<br>AVOW.                                                                               |

| AVRNG-<br>CABFLT<br>CFNRM-<br>CHAN                                                           | Analog voice ring. Cable fault. Cable fault normal.                                                                                                                                                                                                                                    | SG D/R.                                                         | AVOW.<br>AVOW.                                                                                           |

| CABFLT<br>CFNRM-<br>CHAN                                                                     | Cable fault. Cable fault normal.                                                                                                                                                                                                                                                       |                                                                 | AVOW.                                                                                                    |

| CFNRM-<br>CHAN                                                                               | Cable fault normal.                                                                                                                                                                                                                                                                    |                                                                 | _                                                                                                        |

| CHAN                                                                                         |                                                                                                                                                                                                                                                                                        | 1 Tork parion                                                   | AVOW.                                                                                                    |

|                                                                                              | Channal alask (4000 LLL=)                                                                                                                                                                                                                                                              |                                                                 | SG DIR.                                                                                                  |

|                                                                                              | Channel clock (4608 kHz).                                                                                                                                                                                                                                                              | MO/C.                                                           | DGP's.                                                                                                   |

|                                                                                              | Common bus.                                                                                                                                                                                                                                                                            | RAU.                                                            | AVOW.                                                                                                    |

| CNSAUD-                                                                                      | Console audible.                                                                                                                                                                                                                                                                       | AD.                                                             | RAU.                                                                                                     |

| DDCAL-                                                                                       | Digital data call.                                                                                                                                                                                                                                                                     | DDOW decoder.                                                   | AD.                                                                                                      |

| DDCALS                                                                                       | Digital data call signal.                                                                                                                                                                                                                                                              | AD.                                                             | RAU.                                                                                                     |

| DDCLK                                                                                        | Digital data clock (4915.2 kHz).                                                                                                                                                                                                                                                       | MO/C.                                                           | DDOW encoder.                                                                                            |

| DDCT01                                                                                       | DDOW decoder card test loop 1.                                                                                                                                                                                                                                                         |                                                                 | 1                                                                                                        |

| DDCT02                                                                                       | DDOW decoder card test loop 2.                                                                                                                                                                                                                                                         | <sub>1</sub>                                                    | 1                                                                                                        |

| DDCT03                                                                                       | DDOW decoder card test loop 3.                                                                                                                                                                                                                                                         |                                                                 | 1                                                                                                        |

| DDCT04                                                                                       | DDOW decoder card test loop 4.                                                                                                                                                                                                                                                         | 1                                                               | <sup>1</sup><br>  1                                                                                      |

| DDCT05                                                                                       | DDOW decoder card test loop                                                                                                                                                                                                                                                            |                                                                 |                                                                                                          |

| DDI-                                                                                         | Digital data input (ground).                                                                                                                                                                                                                                                           | DDOW encoder.                                                   | RAU.                                                                                                     |

| DDRG-                                                                                        | Digital data ring.                                                                                                                                                                                                                                                                     | RAU.                                                            | DDOW decoder.                                                                                            |

|                                                                                              |                                                                                                                                                                                                                                                                                        |                                                                 | DDOW encoder.                                                                                            |

| DDRV-                                                                                        | Digital data receive.                                                                                                                                                                                                                                                                  | RAU.                                                            | DDOW decoder.                                                                                            |

| DDRY-                                                                                        | Digital data ready.                                                                                                                                                                                                                                                                    | RAU.                                                            | DDOW decoder.                                                                                            |

| DDOD                                                                                         | Digital data and                                                                                                                                                                                                                                                                       | DALL                                                            | DDOW encoder.                                                                                            |

| DDSD-                                                                                        | Digital data send.                                                                                                                                                                                                                                                                     | RAU.                                                            | DDOW decoder. DDOW encoder.                                                                              |

| DECT01                                                                                       | DDOW encoder card test loop 1.                                                                                                                                                                                                                                                         | 1                                                               | 1 DDOW encoder.                                                                                          |

| DECT01                                                                                       | DDOW encoder card test loop 1.  DDOW encoder card test loop 2.                                                                                                                                                                                                                         | ··¦                                                             | 1                                                                                                        |

| DECT02                                                                                       | DDOW encoder card test loop 2.                                                                                                                                                                                                                                                         | ·· <sub>1</sub>                                                 | "1                                                                                                       |

| DECT04                                                                                       | DDOW encoder card test loop 4.                                                                                                                                                                                                                                                         | ·· <sub>1</sub>                                                 | <sub>1</sub>                                                                                             |

| DECT05                                                                                       | DDOW encoder card test loop 5.                                                                                                                                                                                                                                                         | <sub>1</sub>                                                    | "1                                                                                                       |

| DGPCTOX                                                                                      | DGP card test loop 1.                                                                                                                                                                                                                                                                  | 1                                                               | '1                                                                                                       |

| DGPCTOY                                                                                      | DGP card test loop 2.                                                                                                                                                                                                                                                                  | <sub>1</sub>                                                    | '<br>                                                                                                    |

| DMLPS                                                                                        | Dummy lamp.                                                                                                                                                                                                                                                                            | AD.                                                             | Front panel.                                                                                             |

|                                                                                              |                                                                                                                                                                                                                                                                                        |                                                                 | RAU.                                                                                                     |

| DRCT01                                                                                       | SG D/R card test loop 1                                                                                                                                                                                                                                                                | 1                                                               | 1                                                                                                        |

| DRCT02                                                                                       | SG D/R card test loop 2.                                                                                                                                                                                                                                                               | "1<br>"1                                                        | 1<br>                                                                                                    |

| DS                                                                                           | Dummy sync.                                                                                                                                                                                                                                                                            | GTM.                                                            | AD.                                                                                                      |

| DVCAL-                                                                                       | Digital voice call.                                                                                                                                                                                                                                                                    | DVOW.                                                           | AD.                                                                                                      |

| DVCALS                                                                                       | Digital voice call signal.                                                                                                                                                                                                                                                             | AD.                                                             | Front panel.                                                                                             |

| DVCT01                                                                                       | DVOW card test loop 1.                                                                                                                                                                                                                                                                 | 11                                                              | <sup>1</sup>                                                                                             |

| DVCT02                                                                                       | DVOW card test loop 2.                                                                                                                                                                                                                                                                 | ••                                                              | ••                                                                                                       |

| DVEAR                                                                                        | Digital voice earphone.                                                                                                                                                                                                                                                                | DVOW.                                                           | AVOW.                                                                                                    |

| DVEXI                                                                                        | Digital voice extension input.                                                                                                                                                                                                                                                         | RAU.                                                            | DVOW.                                                                                                    |

| DVEXI-                                                                                       | Digital voice extension input (return).                                                                                                                                                                                                                                                | RAU.                                                            | DVOW.                                                                                                    |

| DVEXO                                                                                        | Digital voice extension output.                                                                                                                                                                                                                                                        | DVOW.                                                           | RAU.                                                                                                     |

| DVEXO-                                                                                       | Digital voice extension output (return).                                                                                                                                                                                                                                               | DVOW.                                                           | RAU.                                                                                                     |

| DVMIC                                                                                        | Digital voice microphone.                                                                                                                                                                                                                                                              | AVOW.                                                           | DVOW.                                                                                                    |

| DVDVIC                                                                                       | Digital voice orderwire input.                                                                                                                                                                                                                                                         | DVOW.                                                           | MO/C.<br>AVOW.                                                                                           |

| DVRNG-<br>DVRNGS                                                                             | Digital voice ring. Digital voice ring signal.                                                                                                                                                                                                                                         | AVOW.                                                           | DVOW.                                                                                                    |

| D12EN                                                                                        | Digital data 1200-baud enable.                                                                                                                                                                                                                                                         | DDOW encoder.                                                   | DDOW decoder.                                                                                            |

| D75EN                                                                                        | Digital data 75-baud enable.                                                                                                                                                                                                                                                           | DDOW encoder.                                                   | DDOW decoder.                                                                                            |

| D12I                                                                                         | Digital data 1200-baud input.                                                                                                                                                                                                                                                          | RAU.                                                            | DDOW decoder.  DDOW encoder.                                                                             |

| D75I                                                                                         | Digital data 75-baud input.                                                                                                                                                                                                                                                            | RAU.                                                            | DDOW encoder.                                                                                            |

| See footnotes at end or                                                                      |                                                                                                                                                                                                                                                                                        | 1.5.6.                                                          | 1 22011 01100001.                                                                                        |

| Signal       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                 |

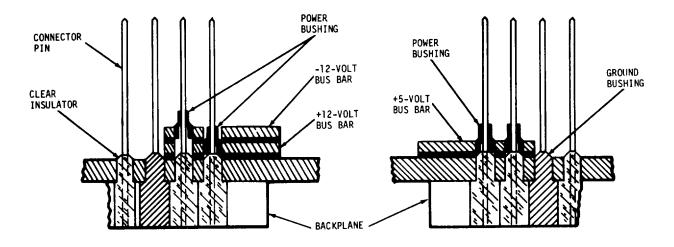

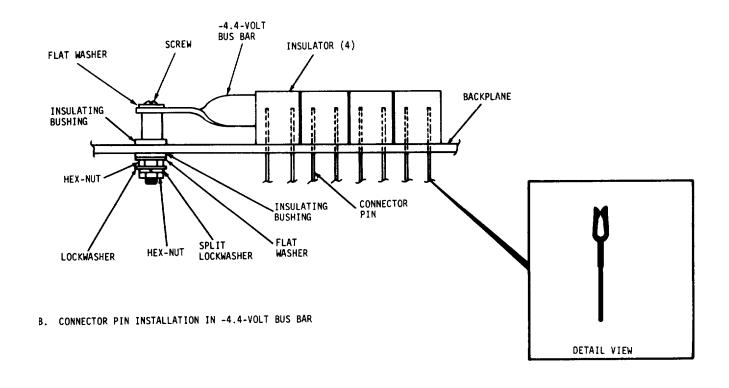

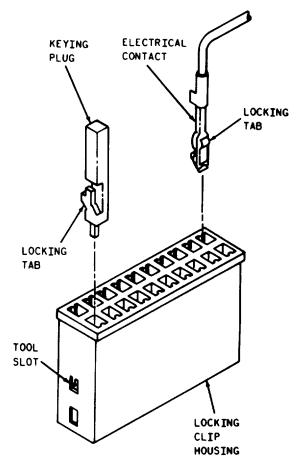

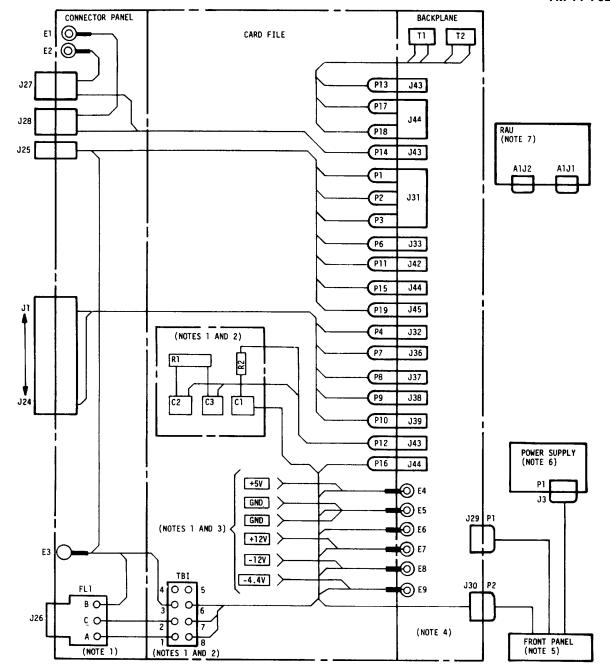

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------|